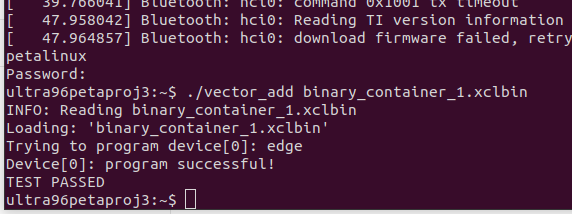

いよいよ最後のVitisです。 2022.2が悪いのか、私がどこかで間違えたのかわかりませんが、めちゃくちゃトラブって時間がかかりました、無事『TEST PASSED』が安定して表示されるようになりました。 自分の備忘録としても重要なので、遭遇したエラー内容と解決方法と、役に立ったデバッグ方法も参考として記載しています。

Vitis インストール

インストールがまだの場合は、『Vitis Unified Software Platform 2022.2インストールと起動方法』をご参照下さい。

Vitis プロジェクト作成

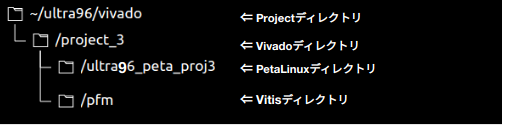

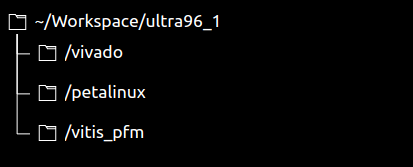

こんな感じで『その3』から作ってきているVitisのプロジェクトのディレクトリ『/pfm』を作ります。 PetaLinuxはプロジェクトを作成する時に、ディレクトリーも作ってくれましたが、Vitisは予めディレクトリを作っておかないといけません。

余談、何もわからず作ったので、上の様な構成になっていますが、本当は以下のような形がいいのかもしれません。 プロジェクトをやり直す時でも、ultra96_1ディレクトリを消すと一発で全てキレイに消せます。 でも、もう上の形で進んできて、動作して検証出来たので、最後まで上のディレクトリ構造で進めていきます。

- 今まで使っているプロジェクトディレクトリに『pfm』ディレクトリを作り、

- Vitisを起動する(ホームディレクトリで起動する)

$ cd ~/ultra96/vivado/project_3 $ mkdir pfm $ cd ~ $ source /tools/Xilinx/Vitis/2022.2/settings64.sh // <---2022.2を2023.1に変えるだけ $ source /tools/Xilinx/Vitis/2022.2/.settings64-Vitis.sh // <---2022.2を2023.1に変えるだけ $ vitis

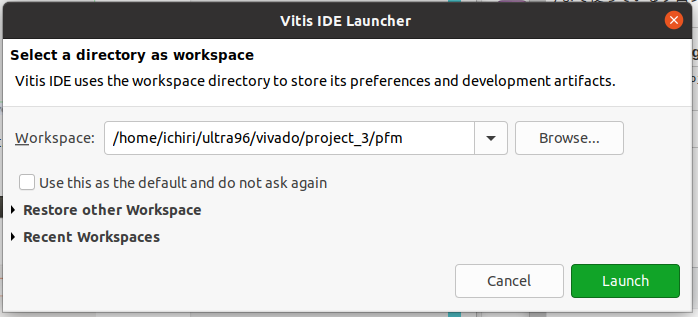

先程作った『pfm』ディレクトリを『Workspace』に指定して『Launch』

Platform Project作成

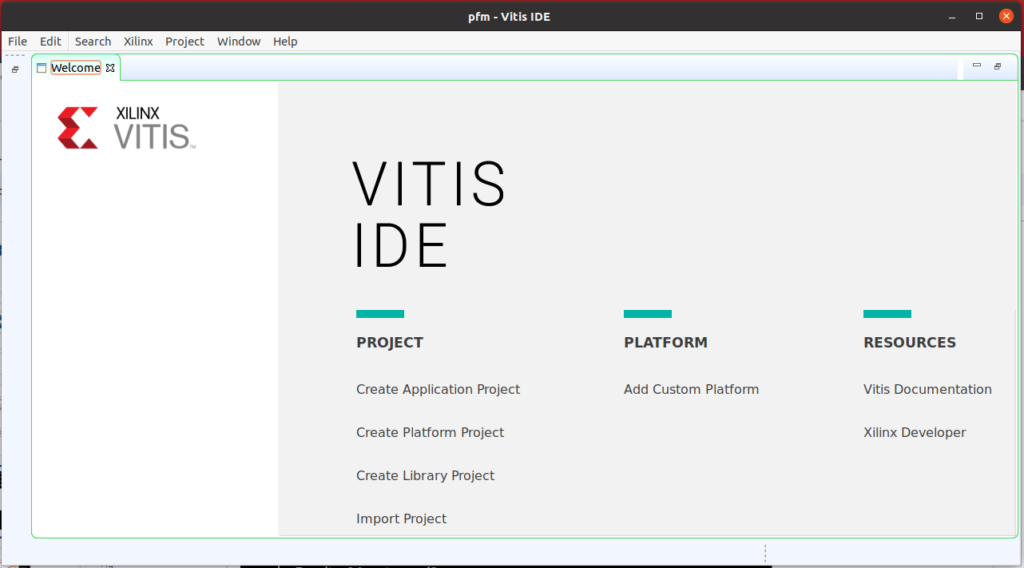

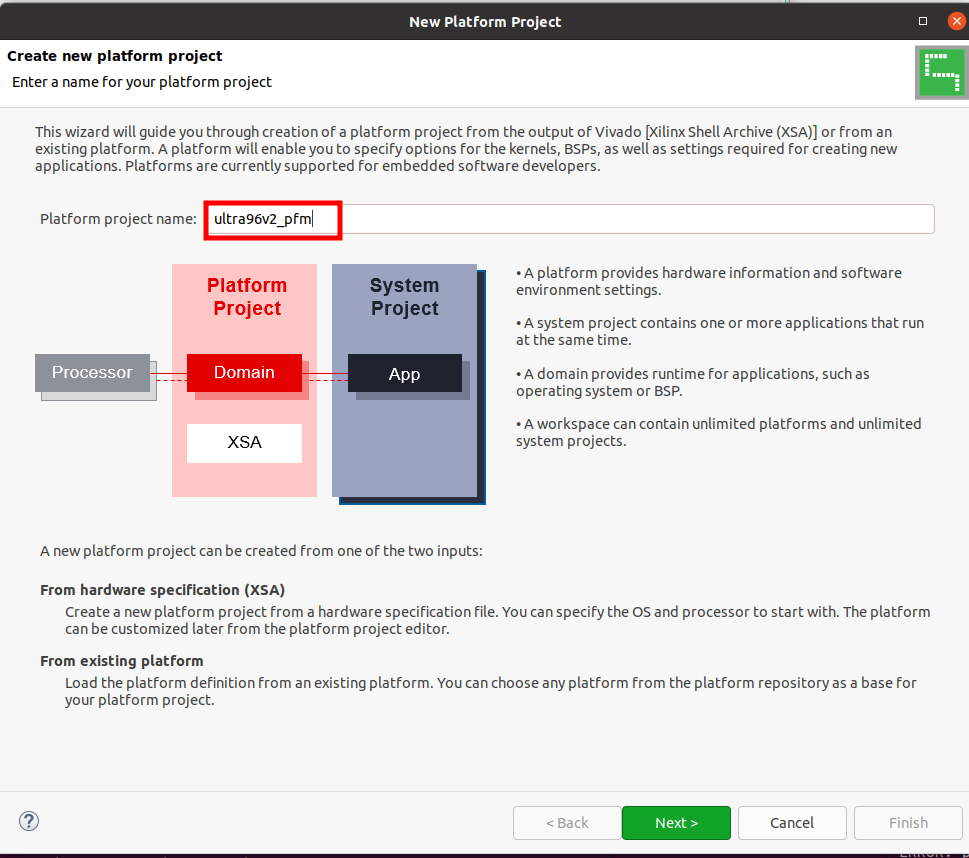

メニューの『File 』〜『New』〜『Platform Project…』を実行。 『Create Platform Project』でも同じと思いますがやってません。 (2023.1も2022.2と全く同じでした。)

『Platform project name』に『ultra96v2_pfm』(任意)と入て『Next』。

(注記).xsaファイル名と.spfmファイル名が同じでなければいけないと何処かに書かれてありましたが。 現在、.xsaファイルは『design_ultra96v2_wrapper.xsa』です。 以下の様に『ultra96v2_pfm』にすると、『./pfm/ultra96v2_pfm/export/ultra96v2_pfm/sw/ultra96v2_pmf.spfm』となり.xsaとファイル名が異なってしまいましたが、vaddは正常に動作しました。

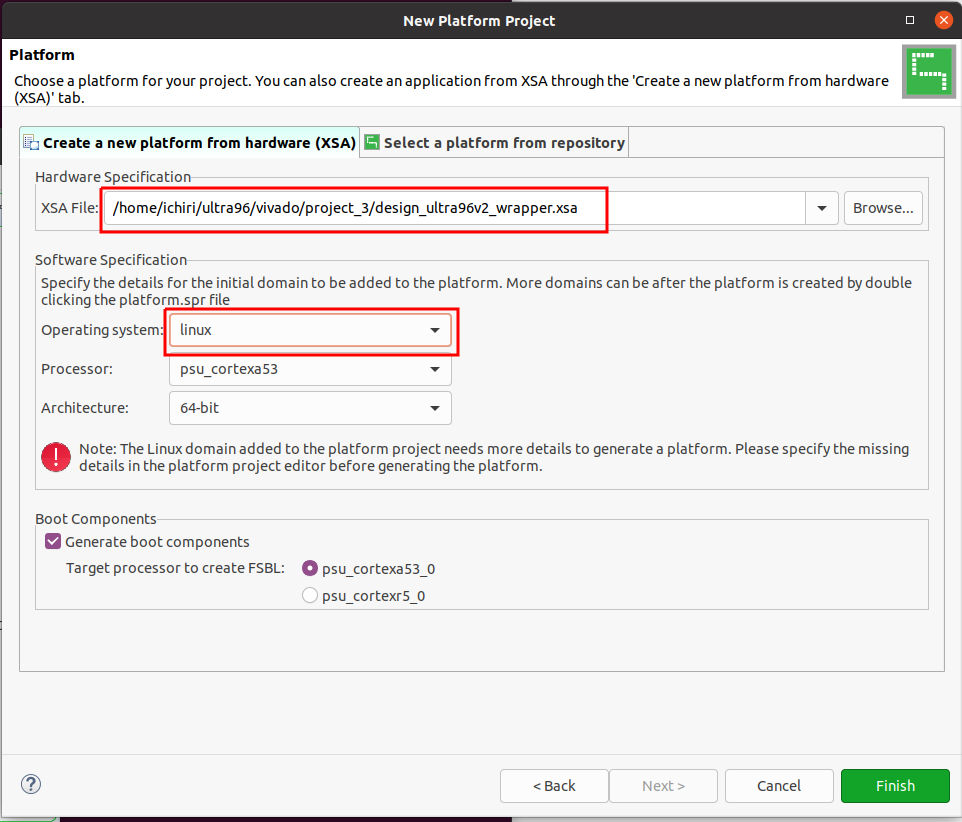

- 『XSA file:』に、Vivadoで作ってある.xsaファイルを『Browse…』から参照する。

- 1分くらい処理していたけど、色々な項目が勝手に読み込まれるので、

- 『Operating System:』で『linux』を選択して

- 『Finish』

- 赤丸の警告マークが表示され『missing details』を指定して下さいと表示されますが、『details』は後ほど入力するので『Finish』で問題ありません。

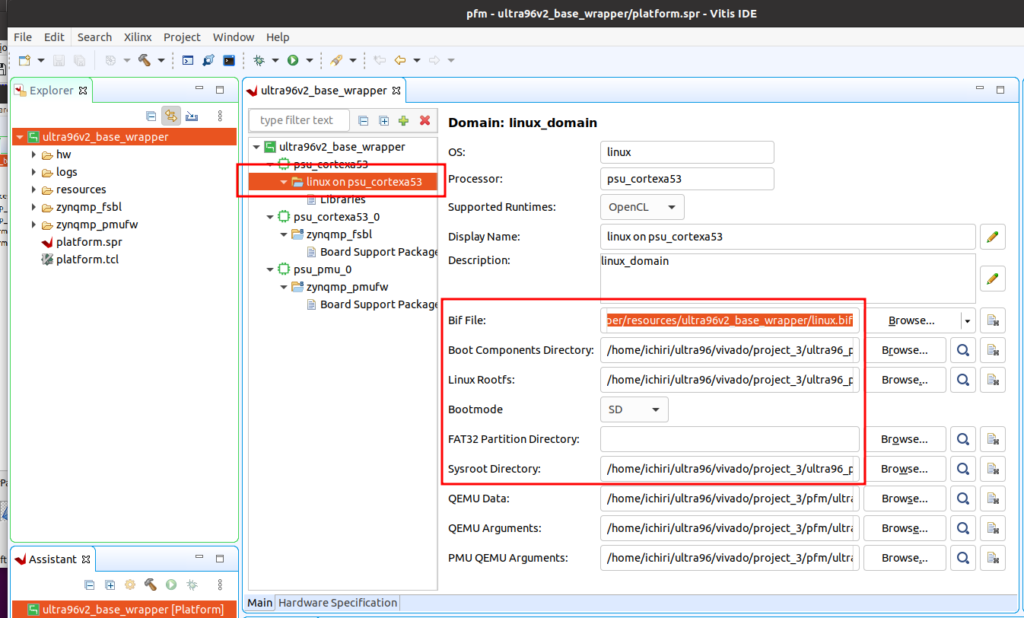

- 下の様な画面が表示されます。

- 『ultra96v2_pfm』タブの下の『linux on psu_cortex53』を選択して赤枠の中を設定する。

- 全て<PETA_PROJ_DIR>の下にあるはず。 私の場合、<PETA_PROJ_DIR>は『~/ultra96/vivado/project_3/ultra96_peta_proj3』

- Bif file: 『Browse』の右の『▼』ボタンをおして『Generate bif』を選択すると自動で作ってくれます。

- Boot Components Directory: <PETA_PROJ_DIR>/images/linux/

- Linux Rootfs: <PETA_PROJ_DIR>/linux_files/boot/rootfs.cpio

- Sysroot Directory: <PETA_PROJ_DIR>/sysroots/cortexa72-cortexa53-xilinx-linux/

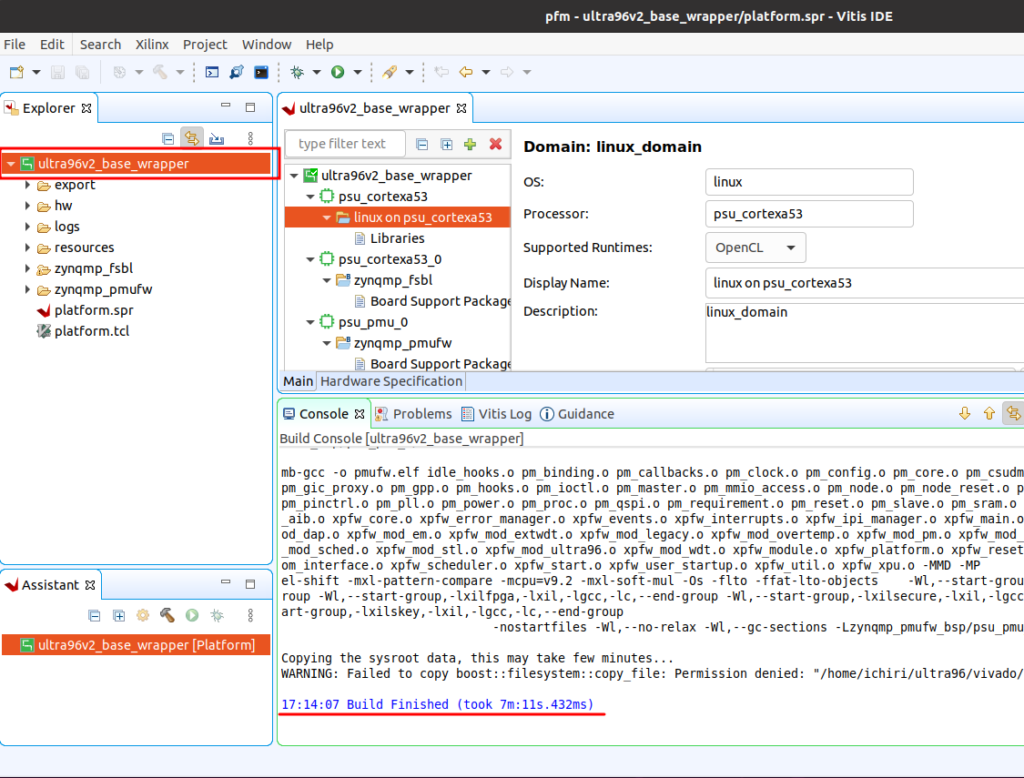

- 左のメニューのプロジェクト名『ultra96v2_pfm』を選んで

- 右クリックして『Build』

- 速いPCなら1分半ほどで終わるようですが、私のPCは7分半かかっています。(新しいPCでは18.3秒でした)

- でもなんとか出来たようです。

- 因みにWarningが出ていますが、sysroots内のsudoの権限が111なので、Read出来なかったのでしょうね。 2020.2等はRead出来たようですが、Warningなので無視して進みます。

Application Project作成

- そのままメニューの『File』〜『New』〜『Application』を選択して、

- 以下のWelcome画面が表示されたら『Next』

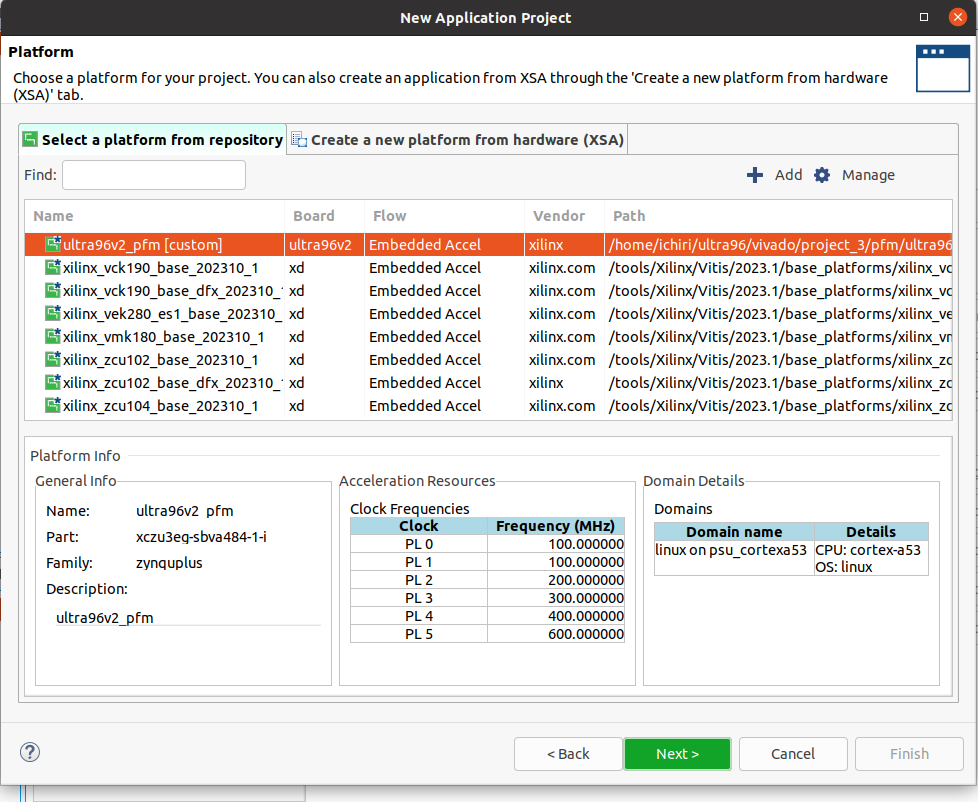

さっき作った『ultra96v2_pfm』を選択して『Next』。 *『その3』のVivadoで作った6個のクロックがちゃんと表示されていますねぇ。

Application project nameに『vector_add』と入力して『Next』

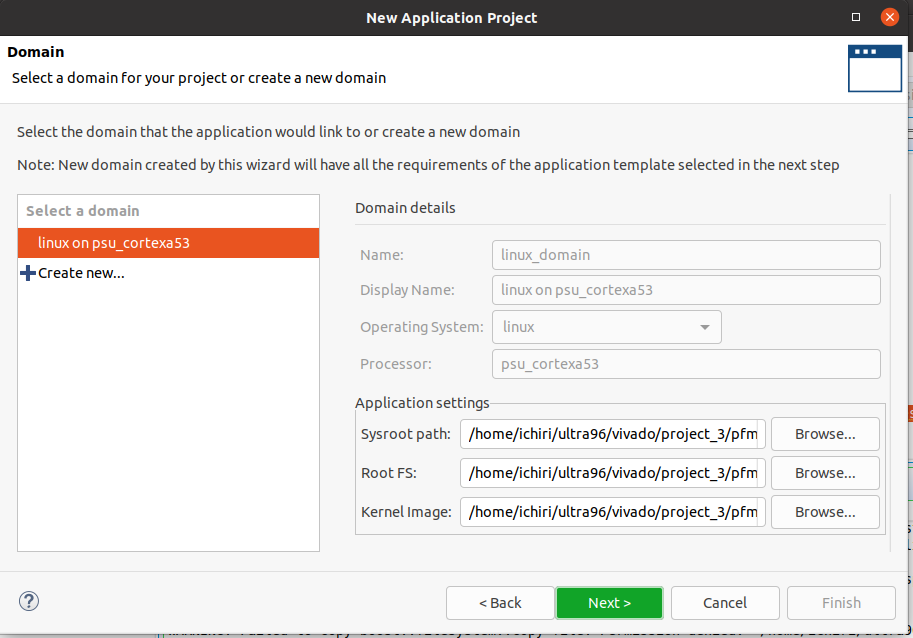

『Next』

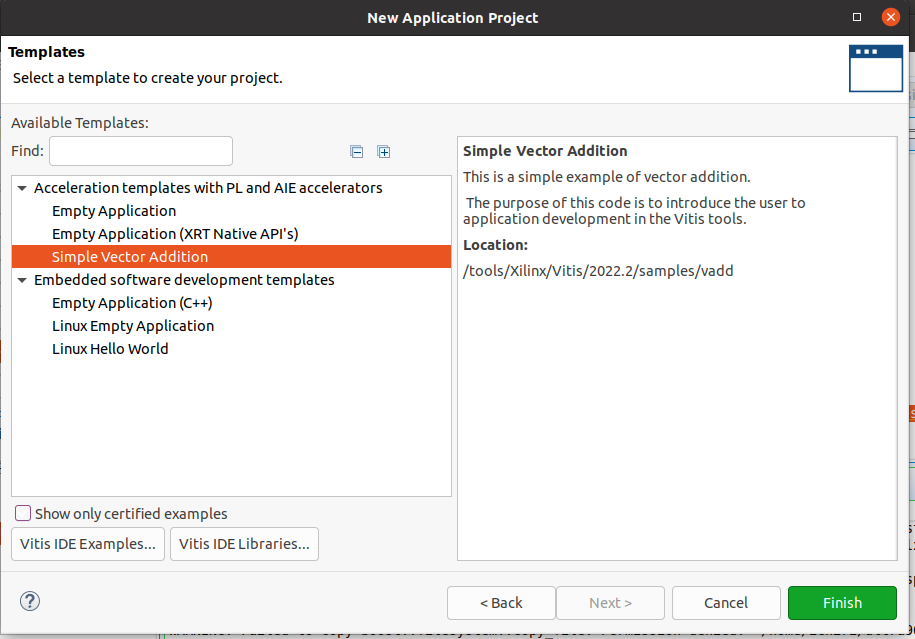

Available Templatesから『Simple Vector Addition』を選択し『Finish』。 *これも2021や2020版とは異なっていますね。(ソースコードも違っていました。)

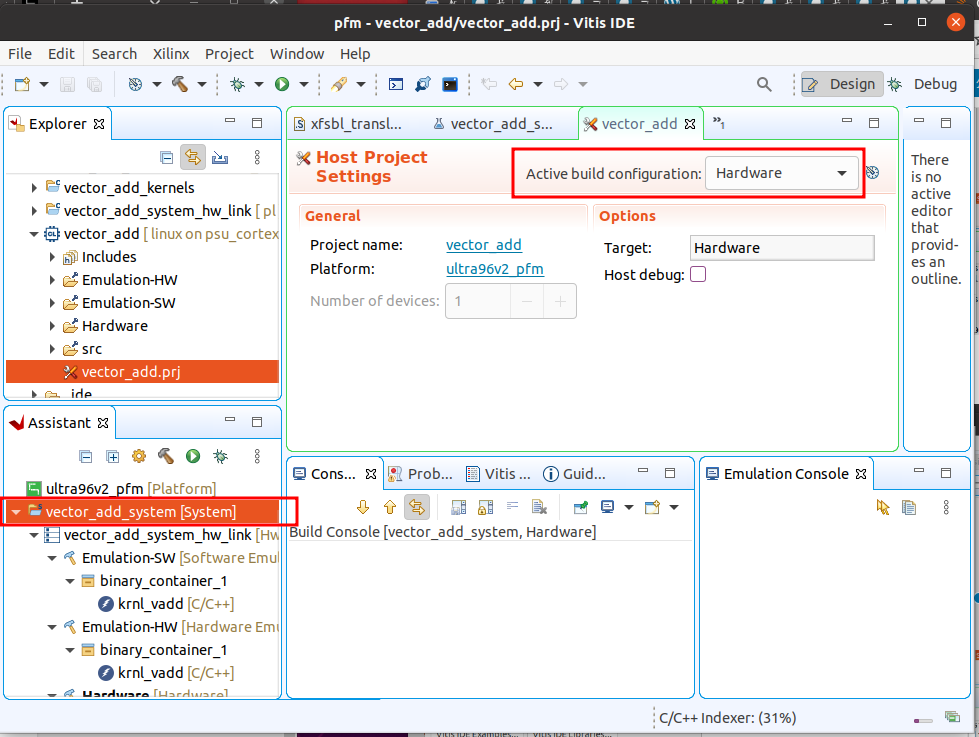

- Active build configuration で『Hardware』を選択して、

- System project nameの『vector_add_system』を選択して、

- その上で右クリックして『Build』を押します。

- しかし、Vitisが『Hardware』を選択して内部的に切り替わるまで時間がかかるようで、『nothing to build』と表示され、ビルドが開始されない場合もあるので、1~2分待って再度『Build』をするとビルドできました。

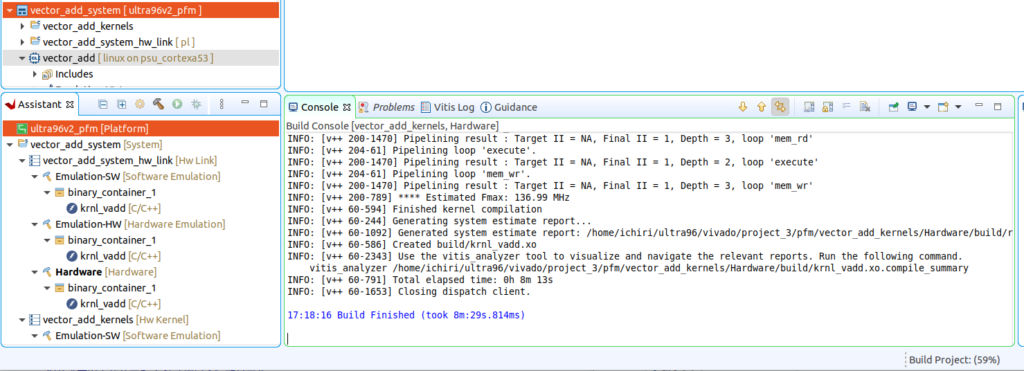

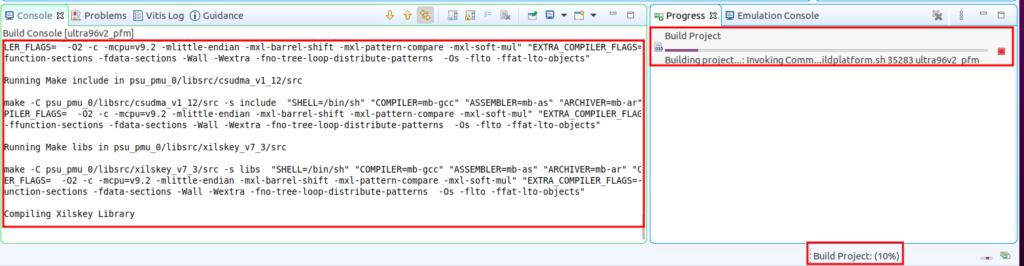

以下のように『Build Finished』となりConsole表示が止まりますが、画面右下には『Build(59%)』となってて、2〜3分したら、またConsole表示が動き出すので、『Build(xx%)』が消えて完了するまで待ちます。 2時間半かかりました。 *Consoleウィンドウの右のウィンドウに経過を示すProgressバーが表示されるので、それも参考にしてました。

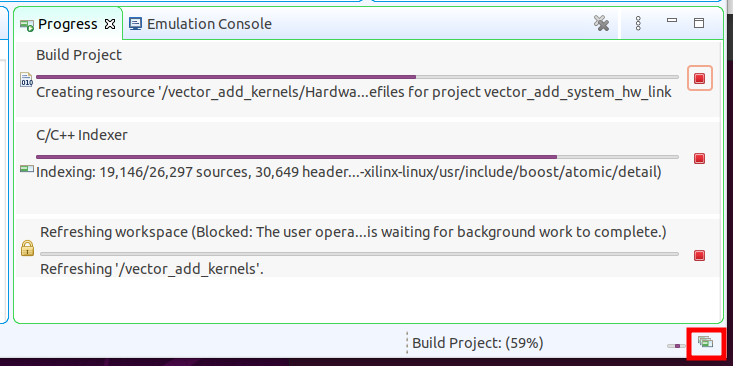

Consoleウィンドウの右下の部分をクリックするとProgressウィンドウでProgressバーが表示されます。

次の作業に入る場合、Progressバーで完了を確認してから次の作業を実施したほうが良さそうです。 常にインデックスを作り直すみたいでしょっちゅうProgressバーが複数表示されています。 少しでも処理を早くしようとしていると思いますが、HDDが早く壊れるかもしれないとびびっています。

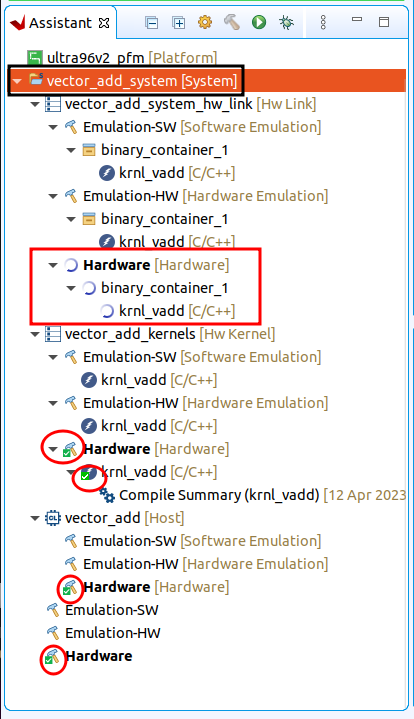

ここを見てもビルド出来たものは赤丸のように緑のチェックマークが付きます。 ビルドを継続している部分は、くるくる回っている様な表示になります。

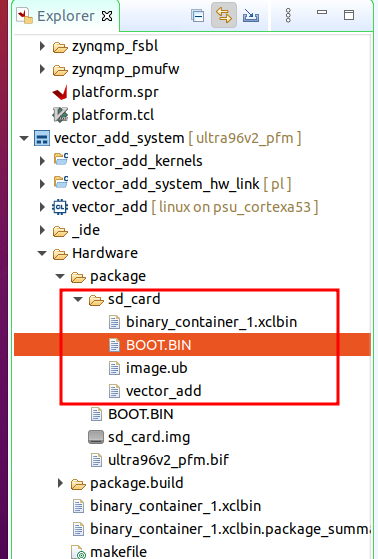

ビルドが成功したら、以下の様に『sd_card』の下に4つのファイルが出来るので、microSDの『BOOT』と『ROOTFS』にそれぞれ以下の様にコピーする。

(*2023.1では、① Refreshがやたら遅いので、中断したらプロジェクトが壊れて、Vitisが立ち上がらなくなった。 私がした対処法は、ここをご参考ください。 ② ビルドが終わっても▶が灰色で開くことができず、Explorerで右クリックしてRefreshを押すと、めちゃくちゃ遅いけど開くことができた。)

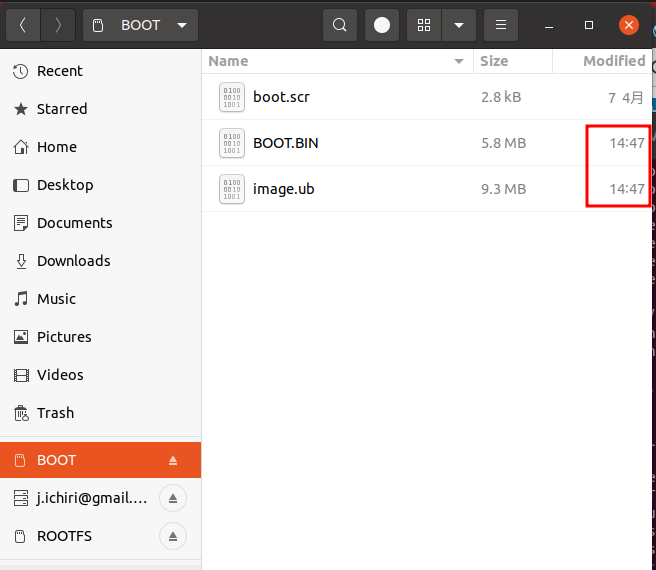

- microSDカードをuBuntu PCに挿して (パーティション作成は『その4』で実施済み)

- 『BOOT』パーティションに以下のファイルをコピーする

- BOOT.BIN — linux.bifを元に作成された。 『その4』で作ったBOOT.BINとは異なります。

- image.ub

- boot.scrは、PetaLinuxがビルドして、『その4』で既にmicroSDに入れてあるものをそのまま使います。

- 『ROOTFS』パーティションの『/home/petalinux/』に以下のファイルをコピーする。

- binary_container_1.xcbin

- bitstream, xrt, krnl_vadd.xoなどが含まれている。

- vaddをFPGA(Compute unitと呼ぶらしい)に作り、vaddへの接続するKernelモジュール(FPGA Kernelと言うらしい)も立ち上げる。

- vector_add — シェル(ユーザー空間)から実行するアプリ。

- binary_container_1.xcbin

- uBuntuのファイルエクスプローラーでコピー&貼り付けしたら簡単でした。 シェルを使う場合は、/mntか/mediaディレクトリの下にディレクトリを作って、microSDの『BOOT』パーティションをマウントしてファイルをコピーしてください。

新しい『BOOT.BIN』と『image.ub』をmicroSDの『BOOT』パーティションに貼り付けたので、下の図のようにタイムスタンプも新しくなっています。 因みに、下の図の5.8MB『BOOT.BIN』では動作せず、動作した『BOOT.BIN』は7.3MBありました。*bif設定を忘れて間違った5.8MBのBOOT.BINが生成されたからでした。

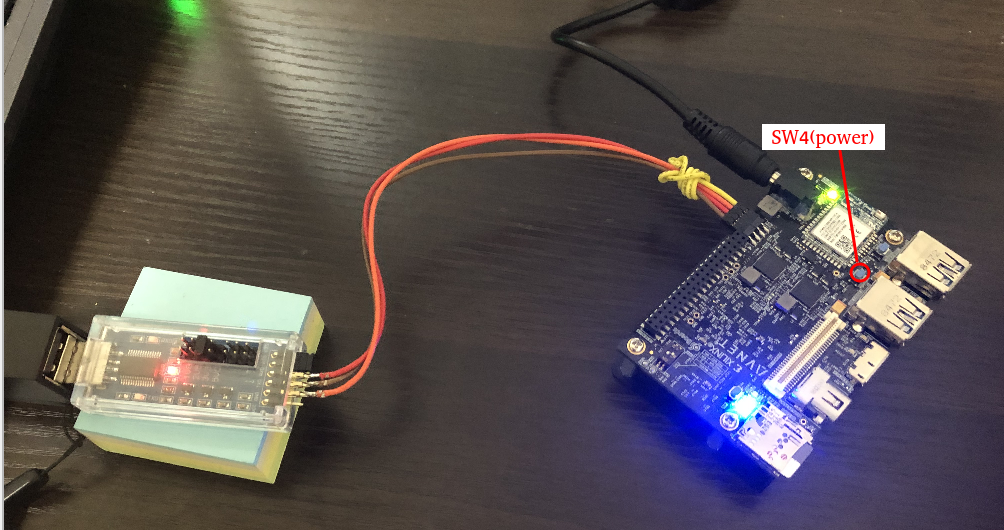

Ultra96V2起動

- microSDをUltra96V2に挿入

- UART-USB変換器をuBuntu PCに装着し、UARTケーブルでUltra96V2と接続する

- uBuntuでminicomを立ち上げる(minicom使い方)115200bps 8N1 *変換器を認識しない時は、ttyUSB名要確認

- Ultra96V2の電源を電源プラグから供給する(LEDが1個だけ点灯する)

- Ultra96V2のSW4を押して起動する(下図参照)(microSDの上のD2 LEDが点灯する)

- うまく起動したら、『login:』が表示されるので、ユーザーID『petalinux』とパスワード(私の場合はこれも『petalinux』)を入力する。(ここまではPetaLinuxと同じ)

- これでpetalinuxユーザー名でホームディレクトリに入ったので、

- ホームディレクトリで以下を実行する

- 『TEST PASSED』とでたら成功です

$ ./vector_add binary_container_1.xcbin

おしまい

参考

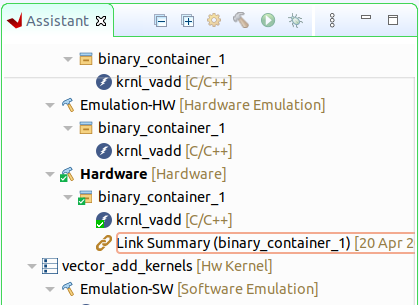

4つのvector_add

Application Projectを『vector_add』にしたら、VitisのExplorerに、『vector_add_system』、『vector_add_system_hw_link』、『vector_add_kernels』、『vector_add』の4つのvector_addで始まるものが出てきました。 調べると以下のようです。

- vector_add_system

- 生成されたFPGAビットストリームファイル(.bit)およびハードウェアプラットフォーム記述ファイル(.hpfm)を含む、Vitisアプリケーションプロジェクト内のディレクトリです。ビットストリームファイルは、FPGAデバイスに書き込まれ、アクセラレーションカーネルが実行されるためのハードウェア構成を指定します。ハードウェアプラットフォーム記述ファイルは、マシンが読み取れる形式でハードウェアプラットフォームを説明します。 Vitisでは親ディレクトリのように表示されていますが、『pfm』ディレクトリ下に他の3つのディレクトリと並列に配置されていました。

- vector_add_system_hw_link

- FPGAデバイスのハードウェアプラットフォームを記述するハードウェアプラットフォーム仕様(HPS)ファイルを含む、Vitisアプリケーションプロジェクト内のディレクトリです。このディレクトリには、ソフトウェアおよびハードウェアコンポーネントをどのようにリンクするかを指定するプラットフォームリンカースクリプトファイル(.ld)も含まれます。

- vector_add_kernels

- カーネルのソースコードファイル、たとえばOpenCLやC++のソースファイル、およびFPGAハードウェアで実行するカーネルをインスタンス化するために使用される生成されたカーネルオブジェクトファイル(.xo)を含む、Vitis/アプリケーションプロジェクト内のディレクトリです。

- vector_add

- Vitisアプリケーションプロジェクトの名前です。このプロジェクトには、FPGAハードウェアとインターフェースし、カーネルを実行するためのメインホストコードが含まれています。

binary_container_1.xclbin

FPGAに書き込まれるBitstreamやKernel等を含んでいるファイル。 全く同じファイルで電源も落とさずに『TEST PASSED』となったり、以下のエラーが出てきたので、binary_container_1.xclbinにkrnl_addのcompute unitを設置するkrnl_add.xoが含まれているか『xclbinutin』か確認。

[XRT] ERROR: No such compute unit 'krnl_vadd:krnl_vadd_1': Invalid argument ../src/vadd.cpp:137 Error calling krnl_vector_add = cl::Kernel(program, "krnl_va dd", &err), error code is: -6

$ source /tools/Xilinx/Vitis/2022.2/settings64.sh $ source /tools/Xilinx/Vitis/2022.2/.settings64-Vitis.sh S xclbinutil --info --input binary_container_1.xclbin

最初のエラー

Vitisで『ultra96v2_pfm』はビルドできましたが、Application Projectの『vector_add』をビルドしたら、以下のエラーとなりました。 要は、『ultra96v2_base_wrapper.dcp』が無いと言っています。(ハイライトされている8行目を横にスクロールしたら出てきます。)

make: *** [makefile:57: binary_container_1.xclbin] Error 1 v++ 60-626: Kernel link failed to complete v++ 60-661: v++ link run 'run_link' failed v++ 60-703: Failed to finish linking VPL 60-1328: Vpl run 'vpl' failed VPL 60-704: Integration error, Failed to rebuild a project required for hardware synthesis. The project is 'prj'. The rebuild script is '.local/hw_platform/prj/rebuild.tcl'. The rebuild script was delivered as part of the hardware platform. Consult with the hardware platform provider to investigate the rebuild script contents. An error stack with function names and arguments may be available in the 'vivado.log'. VPL 60-773] In '/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/vivado/vpl/runme.log', caught Tcl error: ERROR: [Common 17-69: Command failed: File '/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/vivado/vpl/prj/project_3.srcs/utils_1/imports/synth_1/ultra96v2_base_wrapper.dcp' does not exist VPL 60-806: Failed to finish platform linker

Vivadoがdcpファイルを作り、xsaファイルに入れ込んでいるのですが、Vitisも別にdcpファイルを作る為、そのPATHが異なる為このエラーとなるそうです。(以下リンクをご参照下さい) 解決策はVivadoからxsaファイルを作り直します。 その際に、『Settings』で、dcpファイルを作らないと設定して『Export Platform』でxsaを作ります。

『その3』のdisable incremental synthesisで設定して.xsaに.dcpファイルが含まれない様に作りました。

そして、PetaLinuxのプロジェクトも新しく作り直したxsaファイルでビルドし直さなければVitisでApplication Project(vector_add)をビルドする際にエラーになります。

Vivadoで.xsaファイルを作成し直したら、dcpファイルが無いことを確認しましょう。

.xsaファイルはzip形式のアーカイブなので、.xsaを開いて、私の場合は『project_3.srcs/utils_1/imports/synth_1/ultra96v2_base_wrapper.dcp』が無いのを確認しました。

因みに、.xsaファイルを開いて.dcpファイルを削除する事はできましたが、この方法ではVitisでのエラーは解決しませんでした。 あくまでもVivadoで.dcpが.xsaファイルに含まれない様にする必要があります。

また、ultra96v2_base_wrapper.dcpファイル自体は存在していたのですが、Vitisがどうしても違うディレクトリを見に行くので、ディレクトリ名をVitisがultra96v2_base_wrapper.dcpファイルを探しに行くディレクトリ名に変更しても、再度そのディレクトリ名がVitisで書き換えられて解決しませんでした。

ERROR: [VPL 60-773] In '/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/vivado/vpl/runme.log', caught Tcl error: ERROR: [Common 17-69] Command failed: File '/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/vivado/vpl/prj/project_3.srcs/utils_1/imports/synth_1/ultra96v2_base_wrapper.dcp' does not exist //名前を変えた prj.* をproject_3.* ~/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/vivado/vpl/prj$ ls prj.cache prj.gen prj.hw prj.ip_user_files prj.srcs prj.xpr // 以下のメッセージが出るけど Build 59%と表示されている。 その後68%になってまた動き出した 16:59:10 **** Build of configuration Hardware for project vector_add_kernels **** make -j4 all make: Nothing to be done for 'all'. 16:59:11 Build Finished (took 876ms)

2つ目のエラー fsbl.elf is not a file

linux.bifを消してしまっていたので、Vitisが勝手にultra96v2_pfm.bifファイルを作っていたので、エラーが出ました。 PetaLinuxをやり直す時、<PETA_PROJ_DIR>以下を全て削除した時にlinux.bifファイルも消してしまっていました。 『.bif』を作り、Platform Projectに渡す必要があります。

ERROR: [v++ 82-974] /home/ichiri/ultra96/vivado/project_3/pfm/ultra96v2_pfm/export/ultra96v2_pfm/sw/ultra96v2_pfm/boot/fsbl.elf is not a file

../../../../../../images/linux

ERROR: [v++ 82-1002] cannot create bif

// linux.bifを書き忘れていたら、Vitisがultra96v2_pfm.bifを生成し、内容は以下になっていました。

// その為、BOOT.BINが正常に作成されず、それぞれのファイルのPATHも正しく作成されてなかったようです。

$ vi ~/ultra96/vivado/project_3/pfm/ultra96v2_pfm/export/ultra96v2_pfm/sw/ultra96v2_pfm/boot/ultra96v2_pfm.bif

/*ultra96v2_pfm*/

the_ROM_image:

{

[bootloader, destination_cpu=a53-0]<ultra96v2_pfm/boot/fsbl.elf>

[pmufw_image]<ultra96v2_pfm/boot/pmufw.elf>

[destination_device=pl] <bitstream>

}

3つめのエラー No such compute unit ‘krnl_vadd:krnl_vadd_1’

やっと、vaddがビルド出来て『Trying to program device[0]:edge』は『Device[0]: program successful!』で成功したけど以下のエラーが出た。

誰も返信してくれなかったのでこのフォーラムでは解決しませんでしたが、element14のforumにもこのエラーの詳細を投稿しています。(英語)

ultra96petaproj3:~$ ./vector_add binary_container_1.xclbin INFO: Reading binary_container_1.xclbin Loading: 'binary_container_1.xclbin' Trying to program device[0]: edge Device[0]: program successful! XRT build version: 2.14.0 Build hash: 43926231f7183688add2dccfd391b36a1f000bea Build date: 2022-10-07 05:12:02 IDが0のClockがなかったら、Platformを作る時に、ERROR: [CFGEN 83-2299] Clock ID 0 must exist. Please correct the targetted platform.となった。 Git branch: 2022.2 PID: 609 UID: 1000 [Fri Nov 19 17:22:35 2021 GMT] HOST: EXE: /home/petalinux/vector_add [XRT] ERROR: No such compute unit 'krnl_vadd:krnl_vadd_1': Invalid argument ../src/vadd.cpp:137 Error calling krnl_vector_add = cl::Kernel(program, "krnl_va dd", &err), error code is: -6

解決策は、amba_plに接続されてているzyxclmm_drmを検知されないようにsystem-user.dtsiに記述しました。 『その4』PetaLinuxで説明しています。

4つ目のエラー (2023.1のみ)

ERROR: [v++ 82-3593] Template BIF error, malformed braces < >

[bootloader, destination_cpu=a53-0] ./zynqmp_fsbl.elf

ERROR: [v++ 82-1002] cannot create bif

ERROR: [v++ 60-702] Failed to finish packaging

INFO: [v++ 60-1653] Closing dispatch client.

make: *** [makefile:38: package] Error 1

上記エラー時のdmesg

- [ 8.416607]と[ 8.486091]で『xlnx,zocl』が検知され、zoclドライバーとそれぞれマイナー番号1でaxi:zyxclmm_drmと結びついて、マイナー番号2でamba_pl@0:zyxclmm_drmと結びついています。

- 約7回中6回はamba_plを採用して、『./vector_add binary_container_1.xclbin』を実行した時『No such compute unit ‘krnl_vadd:krnl_vadd_1’』エラーとなります。

- なので、amba_plに接続されているzyxclmm_drmを検知されないようにsystem-user.dtsiに記述しました。

[ 3.666554] OF: graph: no port node found in /axi/display@fd4a0000 [ 4.785669] xilinx-axipmon ffa00000.perf-monitor: Probed Xilinx APM [ 4.792214] xilinx-axipmon fd0b0000.perf-monitor: Probed Xilinx APM [ 4.798727] xilinx-axipmon fd490000.perf-monitor: Probed Xilinx APM [ 4.805254] xilinx-axipmon ffa10000.perf-monitor: Probed Xilinx APM [ 8.389921] zocl: loading out-of-tree module taints kernel. [ 8.416607] [drm] Probing for xlnx,zocl [ 8.475493] zocl-drm axi:zyxclmm_drm: IRQ index 32 not found [ 8.485690] [drm] Initialized zocl 0.0.0 00000 for axi:zyxclmm_drm on minor 1 [ 8.486091] [drm] Probing for xlnx,zocl [ 8.486446] zocl-drm amba_pl@0:zyxclmm_drm: IRQ index 32 not found [ 8.527102] [drm] Initialized zocl 0.0.0 00000 for amba_pl@0:zyxclmm_drm on minor 2 //0.0.0はzoclモジュールのバージョン //00000はzoclモジュールのメモリー使用料 //<---amba_pl となっている [ 54.824859] audit: type=1006 audit(1637342417.188:2): pid=591 uid=0 old-auid=4294967295 auid=1000 tty=(none) old-ses=4294967295 ses=1 res=1 [ 54.824900] audit: type=1300 audit(1637342417.188:2): arch=c00000b7 syscall=64 success=yes exit=4 a0=8 a1=ffffc6fe9af0 a2=4 a3=ffffa659f6b0 items=0 ppid=1 pid=591 auid=1000 uid=0 gid=0 euid=0 suid=0 fsuid=0 egid=0 sgid=0 fsgid=0 tty=(none) ses=1 comm="(systemd)" exe="/lib/systemd/systemd" key=(null) [ 54.824913] audit: type=1327 audit(1637342417.188:2): proctitle="(systemd)" [ 91.253992] zocl-drm amba_pl@0:zyxclmm_drm: zocl_create_client: created KDS client for pid(608), ret: 0 [ 91.254103] zocl-drm amba_pl@0:zyxclmm_drm: zocl_destroy_client: client exits pid(608) [ 91.502833] zocl-drm amba_pl@0:zyxclmm_drm: zocl_create_client: created KDS client for pid(608), ret: 0 [ 91.502951] zocl-drm amba_pl@0:zyxclmm_drm: zocl_destroy_client: client exits pid(608) [ 91.503229] zocl-drm amba_pl@0:zyxclmm_drm: zocl_create_client: created KDS client for pid(608), ret: 0 [ 91.563836] [drm] skip kind 29(AIE_RESOURCES) return code: -22 [ 91.563879] [drm] found kind 8(IP_LAYOUT) [ 91.563891] [drm] skip kind 9(DEBUG_IP_LAYOUT) return code: -22 [ 91.563896] [drm] skip kind 25(AIE_METADATA) return code: -22 [ 91.563901] [drm] found kind 7(CONNECTIVITY) [ 91.563908] [drm] found kind 6(MEM_TOPOLOGY) [ 91.564157] [drm] Memory 0 is not reserved in device tree. Will allocate memory from CMA [ 91.564212] [drm] Memory 1 is not reserved in device tree. Will allocate memory from CMA [ 91.564256] [drm] Memory 2 is not reserved in device tree. Will allocate memory from CMA [ 91.564301] [drm] Memory 3 is not reserved in device tree. Will allocate memory from CMA [ 91.564347] [drm] Memory 4 is not reserved in device tree. Will allocate memory from CMA [ 91.564391] [drm] Memory 5 is not reserved in device tree. Will allocate memory from CMA [ 91.565555] zocl_irq_intc ZOCL_CU_INTC.2.auto: zocl_irq_intc_add: managing IRQ 77 [ 91.565653] cu_drv CU.4.auto: cu_probe: CU[0] created [ 91.565791] [drm] zocl_xclbin_read_axlf fcd1d397-d969-99d4-7ddc-1b13fec1a7ad ret: 0 [ 91.579497] [drm] bitstream fcd1d397-d969-99d4-7ddc-1b13fec1a7ad locked, ref=1 [ 91.579555] zocl-drm amba_pl@0:zyxclmm_drm: ffff0000019d3410 kds_add_context: Client pid(608) add context Domain(65535) CU(0xffff) shared(true) [ 91.579620] zocl-drm amba_pl@0:zyxclmm_drm: ffff0000019d3410 kds_del_context: Client pid(608) del context Domain(65535) CU(0xffff) [ 91.579634] [drm] bitstream fcd1d397-d969-99d4-7ddc-1b13fec1a7ad unlocked, ref=0 [ 91.592521] [drm] bitstream fcd1d397-d969-99d4-7ddc-1b13fec1a7ad locked, ref=1 [ 91.592558] zocl-drm amba_pl@0:zyxclmm_drm: ffff0000019d3410 kds_add_context: Client pid(608) add context Domain(65535) CU(0xffff) shared(true) [ 91.617776] zocl-drm amba_pl@0:zyxclmm_drm: ffff0000019d3410 _kds_fini_client: Client pid(608) has open context for 0 slot [ 91.617816] zocl-drm amba_pl@0:zyxclmm_drm: ffff0000019d3410 _kds_fini_client: Removing CU Domain[65535] CU Index [65535] [ 91.617827] zocl-drm amba_pl@0:zyxclmm_drm: ffff0000019d3410 kds_del_context: Client pid(608) del context Domain(65535) CU(0xffff) [ 91.617882] zocl-drm amba_pl@0:zyxclmm_drm: zocl_destroy_client: client exits pid(608)

- system-user.dtsiを変更する前の不安定な状態で成功した時のdmesg内容

- axi:zyxclmm_drmとamba_pl@0:zyxclmm_drmが検知されています

- 何故か、axi:zyxclmm_drmが採用されたので

- [ 23.702277]に、シェルから『./vector_add binary_container_1.xclbin』を実行した時、[ 24.015483]に 『cu_drv CU.4.auto: ffff0000033d8c10 xrt_cu_intr_thread: CU[0] start』とxrt_cu_intr_thread割込イベントでCU.4.auto Compute Unitが認識(接続?)されています。

- CU.4.autoが、『krnl_vadd:krnl_vadd_1』です。

ultra96petaproj3:~$ dmesg |grep -e zocl -e axi [ 3.667939] OF: graph: no port node found in /axi/display@fd4a0000 [ 4.786453] xilinx-axipmon ffa00000.perf-monitor: Probed Xilinx APM [ 4.793005] xilinx-axipmon fd0b0000.perf-monitor: Probed Xilinx APM [ 4.799512] xilinx-axipmon fd490000.perf-monitor: Probed Xilinx APM [ 4.806057] xilinx-axipmon ffa10000.perf-monitor: Probed Xilinx APM [ 8.398943] [drm] Probing for xlnx,zocl [ 8.432261] zocl-drm axi:zyxclmm_drm: IRQ index 32 not found [ 8.472578] [drm] Initialized zocl 0.0.0 00000 for axi:zyxclmm_drm on minor 1 [ 8.473072] [drm] Probing for xlnx,zocl [ 8.473682] zocl-drm amba_pl@0:zyxclmm_drm: IRQ index 32 not found [ 8.488405] [drm] Initialized zocl 0.0.0 00000 for amba_pl@0:zyxclmm_drm on minor 2 [ 3.666554] OF: graph: no port node found in /axi/display@fd4a0000 [ 4.785669] xilinx-axipmon ffa00000.perf-monitor: Probed Xilinx APM [ 4.792214] xilinx-axipmon fd0b0000.perf-monitor: Probed Xilinx APM [ 4.798727] xilinx-axipmon fd490000.perf-monitor: Probed Xilinx APM [ 4.805254] xilinx-axipmon ffa10000.perf-monitor: Probed Xilinx APM [ 8.389921] zocl: loading out-of-tree module taints kernel. [ 8.416607] [drm] Probing for xlnx,zocl [ 8.475493] zocl-drm axi:zyxclmm_drm: IRQ index 32 not found [ 8.485690] [drm] Initialized zocl 0.0.0 00000 for axi:zyxclmm_drm on minor 1 [ 8.486091] [drm] Probing for xlnx,zocl [ 8.486446] zocl-drm amba_pl@0:zyxclmm_drm: IRQ index 32 not found [ 8.527102] [drm] Initialized zocl 0.0.0 00000 for amba_pl@0:zyxclmm_drm on minor 2 [ 23.702277] zocl-drm axi:zyxclmm_drm: zocl_create_client: created KDS client for pid(602), ret: 0 [ 23.702388] zocl-drm axi:zyxclmm_drm: zocl_destroy_client: client exits pid(602) [ 23.951124] zocl-drm axi:zyxclmm_drm: zocl_create_client: created KDS client for pid(602), ret: 0 [ 23.951240] zocl-drm axi:zyxclmm_drm: zocl_destroy_client: client exits pid(602) [ 23.951533] zocl-drm axi:zyxclmm_drm: zocl_create_client: created KDS client for pid(602), ret: 0 [ 24.013522] [drm] skip kind 29(AIE_RESOURCES) return code: -22 [ 24.013566] [drm] found kind 8(IP_LAYOUT) [ 24.013577] [drm] skip kind 9(DEBUG_IP_LAYOUT) return code: -22 [ 24.013583] [drm] skip kind 25(AIE_METADATA) return code: -22 [ 24.013587] [drm] found kind 7(CONNECTIVITY) [ 24.013597] [drm] found kind 6(MEM_TOPOLOGY) [ 24.013842] [drm] Memory 0 is not reserved in device tree. Will allocate memory from CMA [ 24.013891] [drm] Memory 1 is not reserved in device tree. Will allocate memory from CMA [ 24.013936] [drm] Memory 2 is not reserved in device tree. Will allocate memory from CMA [ 24.013982] [drm] Memory 3 is not reserved in device tree. Will allocate memory from CMA [ 24.014028] [drm] Memory 4 is not reserved in device tree. Will allocate memory from CMA [ 24.014071] [drm] Memory 5 is not reserved in device tree. Will allocate memory from CMA [ 24.015090] zocl_irq_intc ZOCL_CU_INTC.2.auto: zocl_irq_intc_add: managing IRQ 77 [ 24.015154] cu_drv CU.4.auto: cu_probe: CU[0] created [ 24.015483] cu_drv CU.4.auto: ffff0000033d8c10 xrt_cu_intr_thread: CU[0] start [ 24.015497] [drm] zocl_xclbin_read_axlf fcd1d397-d969-99d4-7ddc-1b13fec1a7ad ret: 0 [ 24.030062] [drm] bitstream fcd1d397-d969-99d4-7ddc-1b13fec1a7ad locked, ref=1 [ 24.030121] zocl-drm axi:zyxclmm_drm: ffff0000019cb410 kds_add_context: Client pid(602) add context Domain(655 35) CU(0xffff) shared(true) [ 24.030186] zocl-drm axi:zyxclmm_drm: ffff0000019cb410 kds_del_context: Client pid(602) del context Domain(655 35) CU(0xffff) [ 24.030202] [drm] bitstream fcd1d397-d969-99d4-7ddc-1b13fec1a7ad unlocked, ref=0 [ 24.043651] [drm] bitstream fcd1d397-d969-99d4-7ddc-1b13fec1a7ad locked, ref=1 [ 24.043686] zocl-drm axi:zyxclmm_drm: ffff0000019cb410 kds_add_context: Client pid(602) add context Domain(655 35) CU(0xffff) shared(true) [ 24.053823] zocl-drm axi:zyxclmm_drm: ffff0000019cb410 kds_add_context: Client pid(602) add context Domain(0) CU(0x0) shared(true) [ 24.060529] zocl-drm axi:zyxclmm_drm: ffff0000019cb410 kds_del_context: Client pid(602) del context Domain(0) CU(0x0) [ 24.060931] zocl-drm axi:zyxclmm_drm: ffff0000019cb410 kds_del_context: Client pid(602) del context Domain(655 35) CU(0xffff) [ 24.060954] [drm] bitstream fcd1d397-d969-99d4-7ddc-1b13fec1a7ad unlocked, ref=0 [ 24.076573] zocl-drm axi:zyxclmm_drm: zocl_destroy_client: client exits pid(602)

binary_container_1.xclbin 確認

- 『No such compute unit ‘krnl_vadd:krnl_vadd_1’』エラーが出たので、以下のようにbinary_container_1.xclbinの中を確認してみました。

- ユーザー空間の『vector_add』から、『Kernel(program, ‘krnl_vadd’, &err)』で呼び出すKernel空間コマンドの『krnl_vadd』も入っていて (*~/ultra96/vivado/project_3/pfm/vector_add/src/vadd.cppがvector_addに組み込まれていると思う。)

- FPGAに組み込むCompute unitのインスタンスも『krnl_add_1』でアドレス0xa0000000に配置されるようになっているので正しい感じがする

$ xclbinutil --info --input binary_container_1.xclbin

XRT Build Version: 2.14.0 (2022.2)

Build Date: 2022-10-07 05:12:02

Hash ID: 43926231f7183688add2dccfd391b36a1f000bea

------------------------------------------------------------------------------

Warning: The option '--output' has not been specified. All operations will

be done in memory with the exception of the '--dump-section' command.

------------------------------------------------------------------------------

Reading xclbin file into memory. File: binary_container_1.xclbin

==============================================================================

XRT Build Version: 2.14.0 (2022.2)

Build Date: 2022-10-07 05:12:02

Hash ID: 43926231f7183688add2dccfd391b36a1f000bea

==============================================================================

xclbin Information

------------------

Generated by: v++ (2022.2) on 2022-10-13-17:52:11

Version: 2.14.354

Kernels: krnl_vadd

Signature:

Content: Bitstream

UUID (xclbin): 9ad74332-3a47-f4d8-a1fc-436ab3df4930

Sections: BITSTREAM, MEM_TOPOLOGY, IP_LAYOUT, CONNECTIVITY,

BUILD_METADATA, EMBEDDED_METADATA, SYSTEM_METADATA,

GROUP_CONNECTIVITY, GROUP_TOPOLOGY

==============================================================================

Hardware Platform (Shell) Information

-------------------------------------

Vendor: xilinx

Board: ultra96v2

Name: name

Version: 0.0

Generated Version: Vivado 2022.2 (SW Build: 3671981)

Created:

Fri Apr 14 12:25:57 2023 FPGA Device: xczu3eg

Board Vendor: avnet.com

Board Name: avnet.com:ultra96v2:1.2

Board Part: avnet.com:ultra96v2:part0:1.2

Platform VBNV: xilinx_ultra96v2_name_0_0

Static UUID: 00000000-0000-0000-0000-000000000000

Feature ROM TimeStamp: 0

Scalable Clocks

---------------

No scalable clock data available.

System Clocks

------

Name: clk_wiz_0_clk_out1

Type: FIXED

Default Freq: 100 MHz

Name: clk_wiz_0_clk_out2

Type: FIXED

Default Freq: 100 MHz

Name: clk_wiz_0_clk_out3

Type: FIXED

Default Freq: 200 MHz

Name: clk_wiz_0_clk_out4

Type: FIXED

Default Freq: 300 MHz

Name: clk_wiz_0_clk_out5

Type: FIXED

Default Freq: 400 MHz

Name: clk_wiz_0_clk_out6

Type: FIXED

Default Freq: 600 MHz

Memory Configuration

--------------------

Name: HPC0

Index: 0

Type: MEM_DRAM

Base Address: 0x0

Address Size: 0x0

Bank Used: No

Name: HPC1

Index: 1

Type: MEM_DRAM

Base Address: 0x0

Address Size: 0x0

Bank Used: No

Name: HP0

Index: 2

Type: MEM_DRAM

Base Address: 0x0

Address Size: 0x0

Bank Used: No

Name: HP1

Index: 3

Type: MEM_DRAM

Base Address: 0x0

Address Size: 0x0

Bank Used: No

Name: HP2

Index: 4

Type: MEM_DRAM

Base Address: 0x0

Address Size: 0x0

Bank Used: No

Name: HP

Index: 5

Type: MEM_DRAM

Base Address: 0x0

Address Size: 0x80000000

Bank Used: Yes

==============================================================================

Kernel: krnl_vadd

Definition

----------

Signature: krnl_vadd (void* in1, void* in2, void* out, unsigned int size)

Ports

-----

Port: M_AXI_GMEM0

Mode: master

Range (bytes): 0xFFFFFFFF

Data Width: 32 bits

Port Type: addressable

Port: M_AXI_GMEM1

Mode: master

Range (bytes): 0xFFFFFFFF

Data Width: 32 bits

Port Type: addressable

Port: S_AXI_CONTROL

Mode: slave

Range (bytes): 0x3C

Data Width: 32 bits

Port Type: addressable

--------------------------

Instance: krnl_vadd_1

Base Address: 0xa0000000

Argument: in1

Register Offset: 0x10

Port: M_AXI_GMEM0

Memory: HP (MEM_DRAM)

Argument: in2

Register Offset: 0x1C

Port: M_AXI_GMEM1

Memory: HP (MEM_DRAM)

Argument: out

Register Offset: 0x28

Port: M_AXI_GMEM0

Memory: HP (MEM_DRAM)

Argument: size

Register Offset: 0x34

Port: S_AXI_CONTROL

Memory: <not applicable>

==============================================================================

Generated By

Command: v++

Version: 2022.2 - 2022-10-13-17:52:11 (SW BUILD: 3671529)

Command Line: v++ --advanced.misc solution_name=link --config binary_container_1-link.cfg --connectivity.nk krnl_vadd:1:krnl_vadd_1 --input_files ../../vector_add_kernels/Hardware/build/krnl_vadd.xo --link --log_dir binary_container_1.build/logs --messageDb binary_container_1.mdb --optimize 0 --output binary_container_1.xclbin --platform /home/ichiri/ultra96/vivado/project_3/pfm/ultra96v2_pfm/export/ultra96v2_pfm/ultra96v2_pfm.xpfm --remote_ip_cache /home/ichiri/ultra96/vivado/project_3/pfm/ip_cache --report_dir binary_container_1.build/reports --report_level 0 --save-temps --target hw --temp_dir binary_container_1.build

Options: --advanced.misc solution_name=link

--config binary_container_1-link.cfg

--connectivity.nk krnl_vadd:1:krnl_vadd_1

--input_files ../../vector_add_kernels/Hardware/build/krnl_vadd.xo

--link

--log_dir binary_container_1.build/logs

--messageDb binary_container_1.mdb

--optimize 0

--output binary_container_1.xclbin

--platform /home/ichiri/ultra96/vivado/project_3/pfm/ultra96v2_pfm/export/ultra96v2_pfm/ultra96v2_pfm.xpfm

--remote_ip_cache /home/ichiri/ultra96/vivado/project_3/pfm/ip_cache

--report_dir binary_container_1.build/reports

--report_level 0

--save-temps

--target hw

--temp_dir binary_container_1.build

==============================================================================

User Added Key Value Pairs

--------------------------

<empty>

==============================================================================

Leaving xclbinutil.

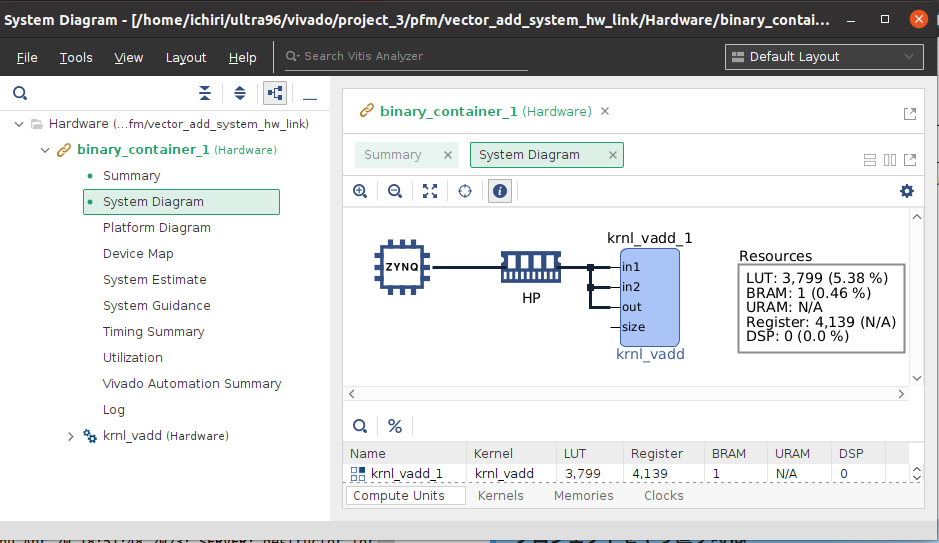

binary_container_1.xclbin確認 その2

『vector_add_syste_hw_link』の下の、『Hardware』の下の『Link Summary(binary_container_1)』をダブルクリックして少し待つとVitis Analyzerで見ることが出来る。

こんな風に見れます。 ちゃんとHP(High Performance)経由でつながってるようになっているので、xclbinは正しいはず。 上記の『xclbinutil –info –input binary_container_1.xclbin』で、HPC0やHP0等は領域が無く、HPしか領域を確保していないので、krnl_vaddを元にkrnl_vadd_1のcompute unitのインスタンスがHPに接続されているのが正しいと思います。 でもkrnl_vadd_1は0xa0000000から始まって、HPは0x0~0x7FFFFFFFなのにそれでいいのかなぁ。 0xa0000000は通常FPGAのロジックが入るデフォルトの先頭番地だそうです。 HPの0x0~0x7FFFFFFFはDDRアクセスアドレスと思うけど。

エラーになる時も、この様に0xa0000000~0xa000003bの0x3c分CU(Compute unit)が入っているのにエラーになる。

$ sudo cat /proc/iomem

Password:

00000000-7fefffff : System RAM

00000000-00000013 : ZOCL_ERT_INTC_STATUS

00000000-00000013 : ZOCL_ERT_INTC_STATUS

00210000-0136ffff : Kernel code

01370000-0157ffff : reserved

01580000-0170ffff : Kernel data

3b800000-7b7fffff : reserved

7bbea000-7bbf4fff : reserved

7d700000-7f9fffff : reserved

7fa69000-7fa69fff : reserved

7fa6a000-7fab1fff : reserved

7fab4000-7fab5fff : reserved

7fab6000-7fab6fff : reserved

7fab7000-7fac7fff : reserved

7fac8000-7fefffff : reserved

a0000000-a000003b : CU.4.auto

:

■

xbutil

- vaddが『TEST PASSED』になって、『xbutil examine -d 0』を実行したら、以下の結果が出てきました。

- PL Compute Unitsの下に『krnl_vadd:kenl_vadd_1』インスタンスが0xa0000000にちゃんと出来ています。

- 『xbutil examine -d 0』はデバイス0(この場合Zynq UltraScale+)の情報を表示します。

- 『xbutil examine -d 0 -r all』とすると全ての情報が表示されます。

- *2020版では使えた『xbutil query』は2022.2ではエラーに、その代わりが『examine』なります。

ultra96petaproj3:~$ xbutil examine -d 0

vitis_freeze

----------------------

[0000:00:00.0] : edge

----------------------

Platform

ERROR: No such query request (151)

Xclbin UUID

FCD1D397-D969-99D4-7DDC-1B13FEC1A7AD

Compute Units

PL Compute Units

Index Name Base_Address Usage Status

0 krnl_vadd:krnl_vadd_1 0xa0000000 1

(IDLE)

PS Compute Units

Index Name Base_Address Usage Status

エラーになった時はこの様になりました。 『krnl_vadd:krnl_vadd_1』が無くなっていますね。 Xclbin UUIDが上記と異なるのは、何度も試したので、ビルドした『binary_container_1.xclbin』が異なるからです。 『xbutil examine -d 0 -r all』にすると全て見える。

ultra96petaproj3:~$ xbutil examine -d 0

----------------------

[0000:00:00.0] : edge

----------------------

Platform

ERROR: No such query request (151)

Xclbin UUID

FCD1D397-D969-99D4-7DDC-1B13FEC1A7AD

Compute Units

PL Compute Units

Index Name Base_Address Usage Status

PS Compute Units

Index Name Base_Address Usage Status

xbutilのヘルプです

■

Vitis用環境変数設定

uBuntuでは以下が必要かも(Xilinx Vitis チュートリアルから)。 何に使うか分からなかったが、今後のために残して起きます。

$ export LIBRARY_PATH= /usr/lib/x86_64-linux-gnu

プロジェクトをやり直す時は

ここも全て検証出来ておらず、何処に載っているかわからないので正しく分ってないかもしれませんが、自分が試した範囲でのメモです。

- Application Projectだけ変更する場合は、Application Projectを削除して再度作成。(Application Projectのディレクトリも削除しないと、同じプロジェクト名は使えない。

- Platform Projectをやり直す時は、Application Projectもやり直す。

- .xsaを変更する場合は、PetaLinuxからビルドし直し、Platform ProjectもApplication Projectもビルドし直しが必要。

.bifファイル

Vitisで.bifファイルをビルドさせると、<VITIS_PROJ_DIR>/vector_add_system/Hardware/package/<platform_name>.bifが以下の内容で生成されてました。

/* linux */

the_ROM_image:

{

[fsbl_config] a53_x64

[bootloader] /home/ichiri/ultra96/vivado/project_3/pfm/ultra96v2_pfm/export/ultra96v2_pfm/sw/ultra96v2_pfm/boot/fsbl.elf

[pmufw_image] /home/ichiri/ultra96/vivado/project_3/pfm/ultra96v2_pfm/export/ultra96v2_pfm/sw/ultra96v2_pfm/boot/pmufw.elf

[destination_device=pl] /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system/Hardware/package.build/package/system.bit

[destination_cpu=a53-0, exception_level=el-3, trustzone] /home/ichiri/ultra96/vivado/project_3/pfm/ultra96v2_pfm/export/ultra96v2_pfm/sw/ultra96v2_pfm/boot/bl31.elf

[load=0x00100000] /home/ichiri/ultra96/vivado/project_3/pfm/ultra96v2_pfm/export/ultra96v2_pfm/sw/ultra96v2_pfm/boot/system.dtb

[destination_cpu=a53-0, exception_level=el-2] /home/ichiri/ultra96/vivado/project_3/pfm/ultra96v2_pfm/export/ultra96v2_pfm/sw/ultra96v2_pfm/boot/u-boot.elf

}

Vitis 2023.1起動画面で固まる

こうなったらどうしようもありません。 もしかしたら5時間くらい放置していたら解決するのかもしれませんが、私の解決方法は

- PCをリブートして

- ホームディレクトリーの『./Xilinx』ディレクトリを消して

- プロジェクトディレクトリ『pfm』を消して、まっさらな『pfm』を作り直して、

- vitisを起動する

固まるパターン

- Progressウィンドウで赤い■マークを何かプロセスをクリックして強制終了した時

- デバイスツリーなど変更してPetaLinuxでKernel、デバイスツリー、ルートファイルシステム、ブートローダ、SDK含め再ビルド後、Vitisプラットフォームは更新せずに、vector_add_system以下を再ビルドした時。この時VitisのInternal ErrorとなってVitisが強制され、Vitisが立ち上がらなくなる。

参考リンク

Vitis Accel examples for 2022.2 from Xilinx

Vitisでビルドした時のログ

将来エラーがでて、正常なログと比較したいときに使おうかなと思います。

17:55:15 **** Build of configuration Hardware for project vector_add_system_hw_link ****

make all

/tools/Xilinx/Vitis/2022.2/bin/v++ --target hw --link --config binary_container_1-link.cfg -o"binary_container_1.xclbin" ../../vector_add_kernels/Hardware/build/krnl_vadd.xo

Option Map File Used: '/tools/Xilinx/Vitis/2022.2/data/vitis/vpp/optMap.xml'

****** v++ v2022.2 (64-bit)

**** SW Build 3671529 on 2022-10-13-17:52:11

** Copyright 1986-2022 Xilinx, Inc. All Rights Reserved.

INFO: [v++ 60-1306] Additional information associated with this v++ link can be found at:

Reports: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/reports/link

Log files: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/logs/link

Running Dispatch Server on port: 42003

INFO: [v++ 60-1548] Creating build summary session with primary output /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.xclbin.link_summary, at Wed Apr 19 17:55:31 2023

INFO: [v++ 60-1315] Creating rulecheck session with output '/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/reports/link/link_guidance.html', at Wed Apr 19 17:55:32 2023

INFO: [v++ 60-895] Target platform: /home/ichiri/ultra96/vivado/project_3/pfm/ultra96v2_base_wrapper/export/ultra96v2_base_wrapper/ultra96v2_base_wrapper.xpfm

INFO: [v++ 60-1578] This platform contains Xilinx Shell Archive '/home/ichiri/ultra96/vivado/project_3/pfm/ultra96v2_base_wrapper/export/ultra96v2_base_wrapper/hw/ultra96v2_base_wrapper.xsa'

INFO: [v++ 60-629] Linking for hardware target

INFO: [v++ 60-423] Target device: ultra96v2_base_wrapper

INFO: [v++ 60-1332] Run 'run_link' status: Not started

INFO: [v++ 60-1443] [17:55:33] Run run_link: Step system_link: Started

INFO: [v++ 60-1453] Command Line: system_link --xo /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_kernels/Hardware/build/krnl_vadd.xo -keep --config /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/syslinkConfig.ini --xpfm /home/ichiri/ultra96/vivado/project_3/pfm/ultra96v2_base_wrapper/export/ultra96v2_base_wrapper/ultra96v2_base_wrapper.xpfm --target hw --output_dir /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int --temp_dir /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link

INFO: [v++ 60-1454] Run Directory: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/run_link

INFO: [SYSTEM_LINK 82-70] Extracting xo v3 file /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_kernels/Hardware/build/krnl_vadd.xo

INFO: [SYSTEM_LINK 82-53] Creating IP database /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link/_sysl/.cdb/xd_ip_db.xml

INFO: [SYSTEM_LINK 82-38] [17:55:39] build_xd_ip_db started: /tools/Xilinx/Vitis/2022.2/bin/build_xd_ip_db -ip_search 0 -sds-pf /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link/ultra96v2_base_wrapper.hpfm -clkid 0 -ip /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link/iprepo/xilinx_com_hls_krnl_vadd_1_0,krnl_vadd -o /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link/_sysl/.cdb/xd_ip_db.xml

INFO: [SYSTEM_LINK 82-37] [17:56:15] build_xd_ip_db finished successfully

Time (s): cpu = 00:00:29 ; elapsed = 00:00:36 . Memory (MB): peak = 449.184 ; gain = 0.000 ; free physical = 2032 ; free virtual = 13870

INFO: [SYSTEM_LINK 82-51] Create system connectivity graph

INFO: [SYSTEM_LINK 82-102] Applying explicit connections to the system connectivity graph: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link/cfgraph/cfgen_cfgraph.xml

INFO: [SYSTEM_LINK 82-38] [17:56:15] cfgen started: /tools/Xilinx/Vitis/2022.2/bin/cfgen -nk krnl_vadd:1:krnl_vadd_1 -dpa_mem_offload false -dmclkid 0 -r /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link/_sysl/.cdb/xd_ip_db.xml -o /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link/cfgraph/cfgen_cfgraph.xml

INFO: [CFGEN 83-0] Kernel Specs:

INFO: [CFGEN 83-0] kernel: krnl_vadd, num: 1 {krnl_vadd_1}

INFO: [CFGEN 83-2226] Inferring mapping for argument krnl_vadd_1.in1 to HP

INFO: [CFGEN 83-2226] Inferring mapping for argument krnl_vadd_1.out to HP

INFO: [CFGEN 83-2226] Inferring mapping for argument krnl_vadd_1.in2 to HP

INFO: [SYSTEM_LINK 82-37] [17:56:19] cfgen finished successfully

Time (s): cpu = 00:00:03 ; elapsed = 00:00:04 . Memory (MB): peak = 449.184 ; gain = 0.000 ; free physical = 2037 ; free virtual = 13877

INFO: [SYSTEM_LINK 82-52] Create top-level block diagram

INFO: [SYSTEM_LINK 82-38] [17:56:19] cf2bd started: /tools/Xilinx/Vitis/2022.2/bin/cf2bd --linux --trace_buffer 1024 --input_file /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link/cfgraph/cfgen_cfgraph.xml --ip_db /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link/_sysl/.cdb/xd_ip_db.xml --cf_name dr --working_dir /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link/_sysl/.xsd --temp_dir /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link --output_dir /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int

INFO: [CF2BD 82-31] Launching cf2xd: cf2xd -linux -trace-buffer 1024 -i /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link/cfgraph/cfgen_cfgraph.xml -r /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link/_sysl/.cdb/xd_ip_db.xml -o dr.xml

INFO: [CF2BD 82-28] cf2xd finished successfully

INFO: [CF2BD 82-31] Launching cf_xsd: cf_xsd -disable-address-gen -dn dr -dp /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/sys_link/_sysl/.xsd

INFO: [CF2BD 82-28] cf_xsd finished successfully

INFO: [SYSTEM_LINK 82-37] [17:56:26] cf2bd finished successfully

Time (s): cpu = 00:00:05 ; elapsed = 00:00:07 . Memory (MB): peak = 449.184 ; gain = 0.000 ; free physical = 2030 ; free virtual = 13875

INFO: [v++ 60-1441] [17:56:26] Run run_link: Step system_link: Completed

Time (s): cpu = 00:00:42 ; elapsed = 00:00:53 . Memory (MB): peak = 465.156 ; gain = 0.000 ; free physical = 2082 ; free virtual = 13927

INFO: [v++ 60-1443] [17:56:26] Run run_link: Step cf2sw: Started

INFO: [v++ 60-1453] Command Line: cf2sw -sdsl /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/sdsl.dat -rtd /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/cf2sw.rtd -nofilter /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/cf2sw_full.rtd -xclbin /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/xclbin_orig.xml -o /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/xclbin_orig.1.xml

INFO: [v++ 60-1454] Run Directory: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/run_link

INFO: [v++ 60-1441] [17:56:32] Run run_link: Step cf2sw: Completed

Time (s): cpu = 00:00:05 ; elapsed = 00:00:06 . Memory (MB): peak = 465.156 ; gain = 0.000 ; free physical = 2073 ; free virtual = 13924

INFO: [v++ 60-1443] [17:56:32] Run run_link: Step rtd2_system_diagram: Started

INFO: [v++ 60-1453] Command Line: rtd2SystemDiagram

INFO: [v++ 60-1454] Run Directory: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/run_link

INFO: [v++ 60-1441] [17:56:32] Run run_link: Step rtd2_system_diagram: Completed

Time (s): cpu = 00:00:00 ; elapsed = 00:00:00.18 . Memory (MB): peak = 465.156 ; gain = 0.000 ; free physical = 2073 ; free virtual = 13924

INFO: [v++ 60-1443] [17:56:32] Run run_link: Step vpl: Started

INFO: [v++ 60-1453] Command Line: vpl -t hw -f /home/ichiri/ultra96/vivado/project_3/pfm/ultra96v2_base_wrapper/export/ultra96v2_base_wrapper/ultra96v2_base_wrapper.xpfm -s --remote_ip_cache /home/ichiri/ultra96/vivado/project_3/pfm/ip_cache --output_dir /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int --log_dir /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/logs/link --report_dir /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/reports/link --config /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/vplConfig.ini -k /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/kernel_info.dat --webtalk_flag Vitis --temp_dir /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link --no-info --iprepo /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/xo/ip_repo/xilinx_com_hls_krnl_vadd_1_0 --messageDb /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/run_link/vpl.pb /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/dr.bd.tcl

INFO: [v++ 60-1454] Run Directory: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/run_link

****** vpl v2022.2 (64-bit)

**** SW Build 3671529 on 2022-10-13-17:52:11

** Copyright 1986-2022 Xilinx, Inc. All Rights Reserved.

INFO: [VPL 60-839] Read in kernel information from file '/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/kernel_info.dat'.

INFO: [VPL 60-423] Target device: ultra96v2_base_wrapper

INFO: [VPL 60-1032] Extracting hardware platform to /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/vivado/vpl/.local/hw_platform

[17:57:06] Run vpl: Step create_project: Started

Creating Vivado project.

[17:57:36] Run vpl: Step create_project: Completed

[17:57:36] Run vpl: Step create_bd: Started

[17:58:07] Run vpl: Step create_bd: Completed

[17:58:07] Run vpl: Step update_bd: Started

[17:58:08] Run vpl: Step update_bd: Completed

[17:58:08] Run vpl: Step generate_target: Started

[17:59:24] Run vpl: Step generate_target: RUNNING...

[18:00:10] Run vpl: Step generate_target: Completed

[18:00:10] Run vpl: Step config_hw_runs: Started

[18:00:19] Run vpl: Step config_hw_runs: Completed

[18:00:19] Run vpl: Step synth: Started

[20:04:28] Top-level synthesis in progress.

[20:06:42] Run vpl: Step synth: Completed

[20:06:43] Run vpl: Step impl: Started

[20:10:53] Finished 2nd of 6 tasks (FPGA linking synthesized kernels to platform). Elapsed time: 02h 14m 15s

[20:10:53] Starting logic optimization..

[20:11:31] Phase 1 Retarget

[20:11:31] Phase 2 Constant propagation

[20:11:31] Phase 3 Sweep

[20:11:31] Phase 4 BUFG optimization

[20:11:31] Phase 5 Shift Register Optimization

[20:11:31] Phase 6 Post Processing Netlist

[20:12:01] Finished 3rd of 6 tasks (FPGA logic optimization). Elapsed time: 00h 01m 08s

[20:12:01] Starting logic placement..

[20:12:01] Phase 1 Placer Initialization

[20:12:01] Phase 1.1 Placer Initialization Netlist Sorting

[20:12:01] Phase 1.2 IO Placement/ Clock Placement/ Build Placer Device

[20:13:02] Phase 1.3 Build Placer Netlist Model

[20:13:02] Phase 1.4 Constrain Clocks/Macros

[20:13:02] Phase 2 Global Placement

[20:13:02] Phase 2.1 Floorplanning

[20:13:33] Phase 2.1.1 Partition Driven Placement

[20:13:33] Phase 2.1.1.1 PBP: Partition Driven Placement

[20:13:33] Phase 2.1.1.2 PBP: Clock Region Placement

[20:13:33] Phase 2.1.1.3 PBP: Compute Congestion

[20:13:33] Phase 2.1.1.4 PBP: UpdateTiming

[20:13:33] Phase 2.1.1.5 PBP: Add part constraints

[20:13:33] Phase 2.2 Update Timing before SLR Path Opt

[20:13:33] Phase 2.3 Post-Processing in Floorplanning

[20:13:33] Phase 2.4 Global Placement Core

[20:14:03] Phase 2.4.1 UpdateTiming Before Physical Synthesis

[20:14:03] Phase 2.4.2 Physical Synthesis In Placer

[20:14:03] Phase 3 Detail Placement

[20:14:03] Phase 3.1 Commit Multi Column Macros

[20:14:03] Phase 3.2 Commit Most Macros & LUTRAMs

[20:14:34] Phase 3.3 Small Shape DP

[20:14:34] Phase 3.3.1 Small Shape Clustering

[20:14:34] Phase 3.3.2 Flow Legalize Slice Clusters

[20:14:34] Phase 3.3.3 Slice Area Swap

[20:14:34] Phase 3.3.3.1 Slice Area Swap Initial

[20:14:34] Phase 3.4 Re-assign LUT pins

[20:14:34] Phase 3.5 Pipeline Register Optimization

[20:14:34] Phase 4 Post Placement Optimization and Clean-Up

[20:14:34] Phase 4.1 Post Commit Optimization

[20:15:05] Phase 4.1.1 Post Placement Optimization

[20:15:05] Phase 4.1.1.1 BUFG Insertion

[20:15:05] Phase 1 Physical Synthesis Initialization

[20:15:05] Phase 4.1.1.2 Post Placement Timing Optimization

[20:15:05] Phase 4.2 Post Placement Cleanup

[20:15:05] Phase 4.3 Placer Reporting

[20:15:05] Phase 4.3.1 Print Estimated Congestion

[20:15:05] Phase 4.4 Final Placement Cleanup

[20:15:35] Finished 4th of 6 tasks (FPGA logic placement). Elapsed time: 00h 03m 34s

[20:15:35] Starting logic routing..

[20:15:35] Phase 1 Build RT Design

[20:15:35] Phase 2 Router Initialization

[20:15:35] Phase 2.1 Fix Topology Constraints

[20:15:35] Phase 2.2 Pre Route Cleanup

[20:15:35] Phase 2.3 Global Clock Net Routing

[20:16:06] Phase 2.4 Update Timing

[20:16:06] Phase 3 Initial Routing

[20:16:06] Phase 3.1 Global Routing

[20:16:37] Phase 4 Rip-up And Reroute

[20:16:37] Phase 4.1 Global Iteration 0

[20:17:38] Phase 4.2 Additional Iteration for Hold

[20:17:38] Phase 5 Delay and Skew Optimization

[20:17:38] Phase 5.1 Delay CleanUp

[20:17:38] Phase 5.1.1 Update Timing

[20:17:38] Phase 5.1.2 Update Timing

[20:17:38] Phase 5.2 Clock Skew Optimization

[20:17:38] Phase 6 Post Hold Fix

[20:17:38] Phase 6.1 Hold Fix Iter

[20:17:38] Phase 6.1.1 Update Timing

[20:17:38] Phase 7 Route finalize

[20:18:09] Phase 8 Verifying routed nets

[20:18:09] Phase 9 Depositing Routes

[20:18:09] Phase 10 Resolve XTalk

[20:18:09] Phase 11 Post Router Timing

[20:18:09] Finished 5th of 6 tasks (FPGA routing). Elapsed time: 00h 02m 33s

[20:18:09] Starting bitstream generation..

[20:19:10] Creating bitmap...

[20:19:10] Writing bitstream ./ultra96v2_base_wrapper.bit...

[20:19:10] Finished 6th of 6 tasks (FPGA bitstream generation). Elapsed time: 00h 01m 01s

Check VPL, containing 1 checks, has run: 0 errors

[20:19:23] Run vpl: Step impl: Completed

[20:19:24] Run vpl: FINISHED. Run Status: impl Complete!

INFO: [v++ 60-1441] [20:19:41] Run run_link: Step vpl: Completed

Time (s): cpu = 00:00:59 ; elapsed = 02:23:09 . Memory (MB): peak = 465.156 ; gain = 0.000 ; free physical = 3815 ; free virtual = 12384

INFO: [v++ 60-1443] [20:19:42] Run run_link: Step rtdgen: Started

INFO: [v++ 60-1453] Command Line: rtdgen

INFO: [v++ 60-1454] Run Directory: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/run_link

INFO: [v++ 60-1453] Command Line: cf2sw -a /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/address_map.xml -sdsl /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/sdsl.dat -xclbin /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/xclbin_orig.xml -rtd /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/binary_container_1.rtd -o /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/binary_container_1.xml

INFO: [v++ 60-1652] Cf2sw returned exit code: 0

INFO: [v++ 60-1441] [20:19:50] Run run_link: Step rtdgen: Completed

Time (s): cpu = 00:00:04 ; elapsed = 00:00:09 . Memory (MB): peak = 465.156 ; gain = 0.000 ; free physical = 3766 ; free virtual = 12367

INFO: [v++ 60-1443] [20:19:51] Run run_link: Step xclbinutil: Started

INFO: [v++ 60-1453] Command Line: xclbinutil --add-section BITSTREAM:RAW:/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/system.bit --force --target hw --key-value SYS:dfx_enable:false --add-section :JSON:/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/binary_container_1.rtd --add-section CLOCK_FREQ_TOPOLOGY:JSON:/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/binary_container_1_xml.rtd --add-section BUILD_METADATA:JSON:/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/binary_container_1_build.rtd --add-section EMBEDDED_METADATA:RAW:/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/binary_container_1.xml --add-section SYSTEM_METADATA:RAW:/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/systemDiagramModelSlrBaseAddress.json --key-value SYS:PlatformVBNV:xilinx_ultra96v2_name_0_0 --output /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.xclbin

INFO: [v++ 60-1454] Run Directory: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/run_link

XRT Build Version: 2.14.354 (2022.2)

Build Date: 2022-10-08 09:49:58

Hash ID: 43926231f7183688add2dccfd391b36a1f000bea

Creating a default 'in-memory' xclbin image.

Section: 'BITSTREAM'(0) was successfully added.

Size : 5568794 bytes

Format : RAW

File : '/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/system.bit'

Section: 'MEM_TOPOLOGY'(6) was successfully added.

Format : JSON

File : 'mem_topology'

Section: 'IP_LAYOUT'(8) was successfully added.

Format : JSON

File : 'ip_layout'

Section: 'CONNECTIVITY'(7) was successfully added.

Format : JSON

File : 'connectivity'

WARNING: Skipping CLOCK_FREQ_TOPOLOGY section for count size is zero.

WARNING: Section 'CLOCK_FREQ_TOPOLOGY' content is empty. No data in the given JSON file.

Section: 'CLOCK_FREQ_TOPOLOGY'(11) was empty. No action taken.

Format : JSON

File : '/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/binary_container_1_xml.rtd'

Section: 'BUILD_METADATA'(14) was successfully added.

Size : 2629 bytes

Format : JSON

File : '/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/binary_container_1_build.rtd'

Section: 'EMBEDDED_METADATA'(2) was successfully added.

Size : 8701 bytes

Format : RAW

File : '/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/binary_container_1.xml'

Section: 'SYSTEM_METADATA'(22) was successfully added.

Size : 12623 bytes

Format : RAW

File : '/home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/int/systemDiagramModelSlrBaseAddress.json'

Successfully wrote (5600659 bytes) to the output file: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.xclbin

Leaving xclbinutil.

INFO: [v++ 60-1441] [20:19:54] Run run_link: Step xclbinutil: Completed

Time (s): cpu = 00:00:00.18 ; elapsed = 00:00:03 . Memory (MB): peak = 465.156 ; gain = 0.000 ; free physical = 3757 ; free virtual = 12367

INFO: [v++ 60-1443] [20:19:54] Run run_link: Step xclbinutilinfo: Started

INFO: [v++ 60-1453] Command Line: xclbinutil --quiet --force --info /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.xclbin.info --input /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.xclbin

INFO: [v++ 60-1454] Run Directory: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/run_link

INFO: [v++ 60-1441] [20:19:54] Run run_link: Step xclbinutilinfo: Completed

Time (s): cpu = 00:00:00.33 ; elapsed = 00:00:00.5 . Memory (MB): peak = 465.156 ; gain = 0.000 ; free physical = 3762 ; free virtual = 12374

INFO: [v++ 60-1443] [20:19:54] Run run_link: Step generate_sc_driver: Started

INFO: [v++ 60-1453] Command Line:

INFO: [v++ 60-1454] Run Directory: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/link/run_link

INFO: [v++ 60-1441] [20:19:54] Run run_link: Step generate_sc_driver: Completed

Time (s): cpu = 00:00:00 ; elapsed = 00:00:00.15 . Memory (MB): peak = 465.156 ; gain = 0.000 ; free physical = 3762 ; free virtual = 12374

Check POST-VPL, containing 1 checks, has run: 0 errors

INFO: [v++ 60-244] Generating system estimate report...

INFO: [v++ 60-1092] Generated system estimate report: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/reports/link/system_estimate_binary_container_1.xtxt

INFO: [v++ 60-2397] Platform default or user specified output type sd_card detected but is not a supported output for v++ --link. Use the v++ --package option instead to create SD card output.

INFO: [v++ 60-586] Created binary_container_1.xclbin

INFO: [v++ 60-1307] Run completed. Additional information can be found in:

Guidance: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/reports/link/link_guidance.html

Timing Report: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/reports/link/imp/impl_1_ultra96v2_base_wrapper_timing_summary_routed.rpt

Vivado Log: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/logs/link/vivado.log

Steps Log File: /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.build/logs/link/link.steps.log

INFO: [v++ 60-2343] Use the vitis_analyzer tool to visualize and navigate the relevant reports. Run the following command.

vitis_analyzer /home/ichiri/ultra96/vivado/project_3/pfm/vector_add_system_hw_link/Hardware/binary_container_1.xclbin.link_summary

INFO: [v++ 60-791] Total elapsed time: 2h 24m 37s

INFO: [v++ 60-1653] Closing dispatch client.

20:20:24 Build Finished (took 2h:25m:9s.434ms)

binary_container_1.xclbinをFPGAに書込

$ xbutil program -u binary_container_1.xclbin -d 0

$ xbutil examine -r memory -d 0

----------------------

[0000:00:00.0] : edge

----------------------

Memory Topology

Tag Type Temp(C) Size Base Address

[ 0] HPC0 MEM_DRAM N/A 0 Byte 0x0

[ 1] HPC1 MEM_DRAM N/A 0 Byte 0x0

[ 2] HP0 MEM_DRAM N/A 0 Byte 0x0

[ 3] HP1 MEM_DRAM N/A 0 Byte 0x0

[ 4] HP2 MEM_DRAM N/A 0 Byte 0x0

[ 5] HP MEM_DRAM N/A 2 GB 0x0

COMMAND: program

DESCRIPTION: Programs the given acceleration image into the device’s shell.

USAGE: xbutil program [-h] –[ ] [commandArgs]

OPTIONS:

-d, –device – The Bus:Device.Function (e.g., 0000:d8:00.0) device of interest.

-u, –user – The name (and path) of the xclbin to be loaded

–help – Help to use this sub-command

GLOBAL OPTIONS:

–verbose – Turn on verbosity

–batch – Enable batch mode (disables escape characters)

–force – When possible, force an operation

ultra96petaproj3:~$

コメント