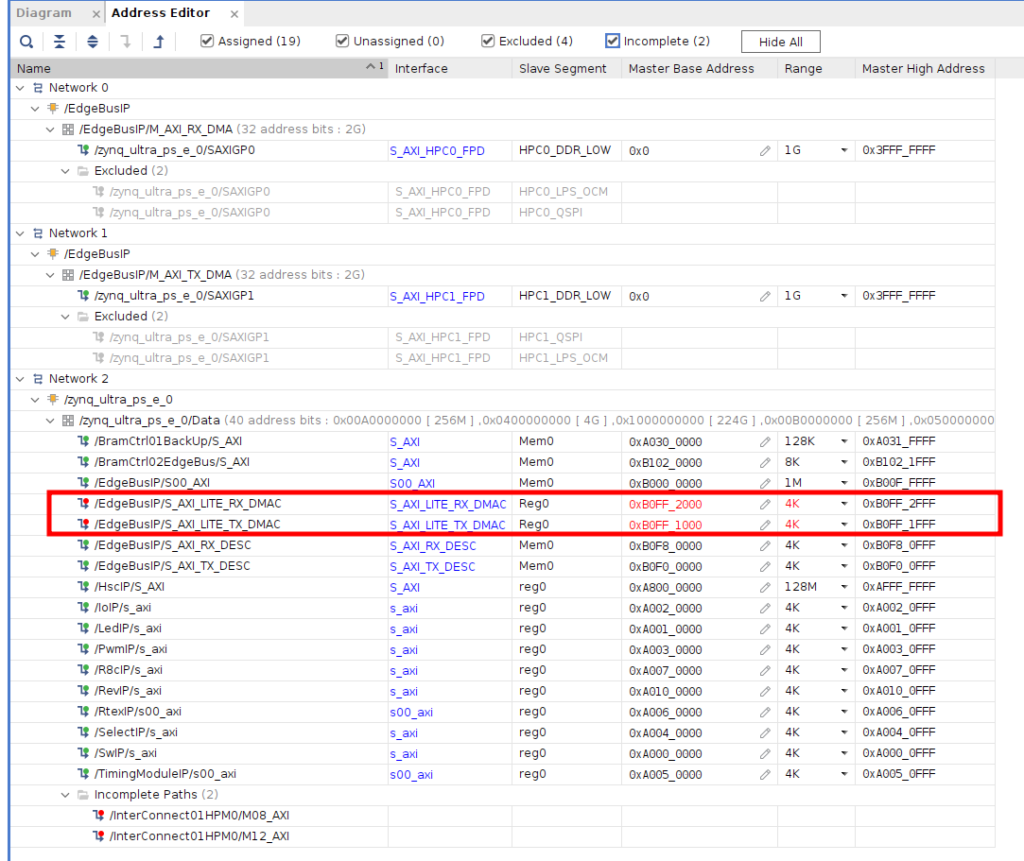

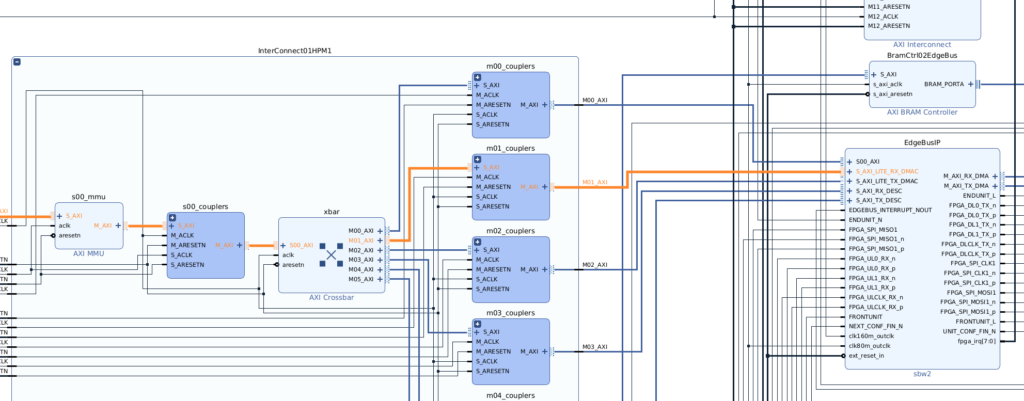

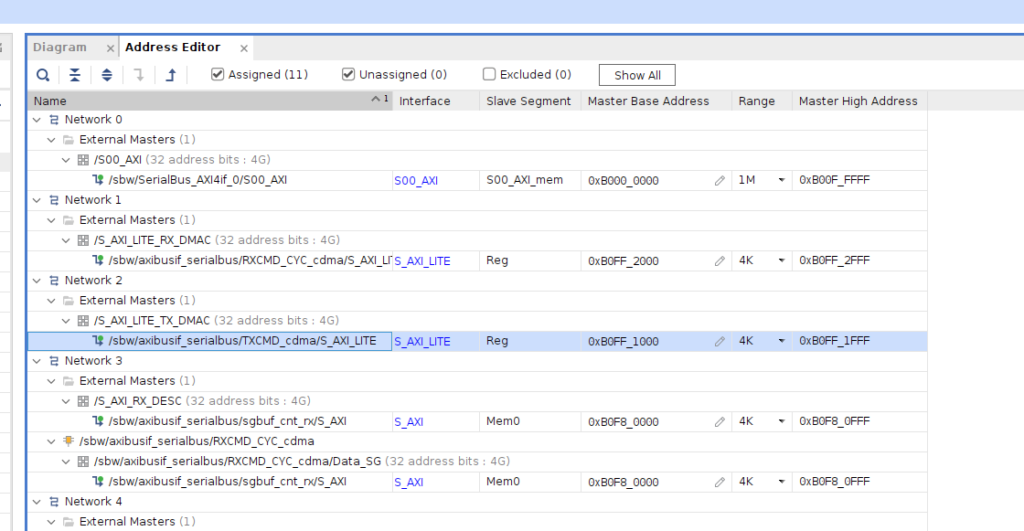

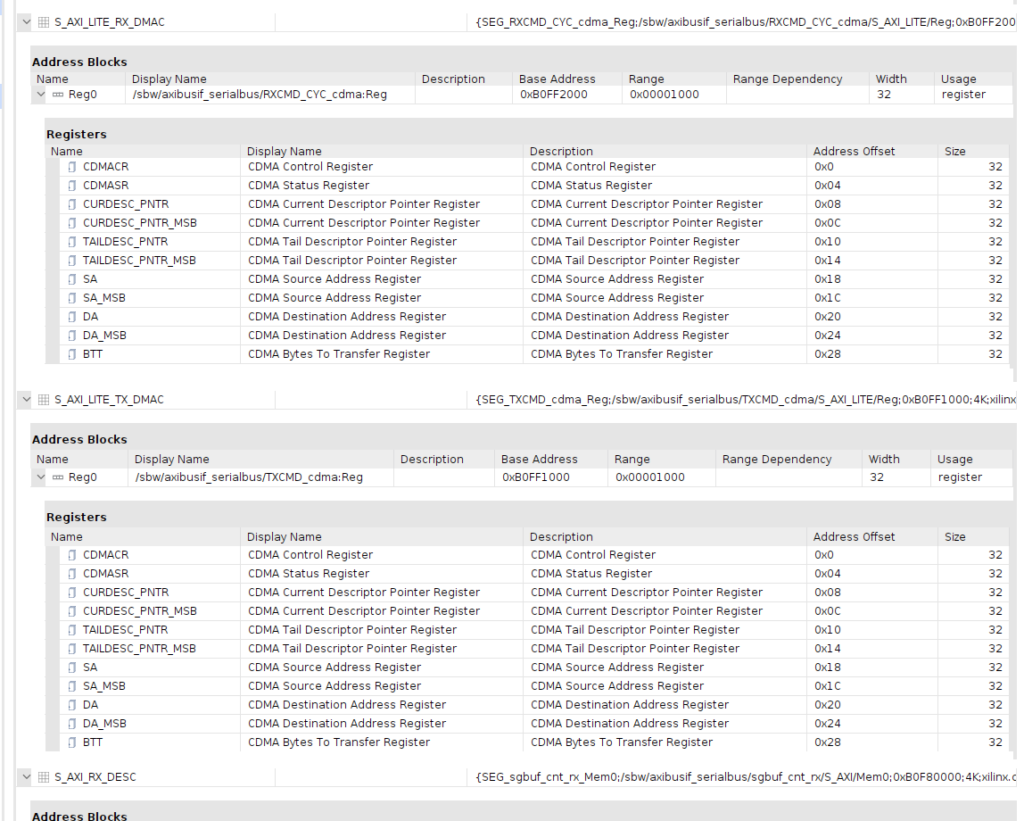

When I convert a project made by Vivado2019.2 to Vivado2022.2 or 2023.1, the below two error showed up and was not able to finish synthesis. It seems that the addresses of the two ports on EdgeBusIP were somewhat not assigned to the master memory map, which Vivado calls “Aperture”. But the addresses of other three ports on the same EdgeBusIP were assigned in the master memory map.

[BD 41-1075] Cannot assign slave segment '/EdgeBusIP/S_AXI_LITE_RX_DMAC/Reg0' into address space '/zynq_ultra_ps_e_0/Data' at address '0xB0FF_2000 [ 4K ]'. Master segment '/zynq_ultra_ps_e_0/Data/SEG_EdgeBusIP_Reg0' is invalid. The proposed logical address '0xB0FF_2000 [ 4K ]' remaps to physical address '0x0000_0000 [ 4K ]' which must be equivalent to the physical fixed address '0xB0FF_2000 [ 4K ]' of slave segment '/EdgeBusIP/S_AXI_LITE_RX_DMAC/Reg0'. Please assign a physical offset whose '32' least significant bits match '0xB0FF_2000'. [BD 41-1075] Cannot assign slave segment '/EdgeBusIP/S_AXI_LITE_TX_DMAC/Reg0' into address space '/zynq_ultra_ps_e_0/Data' at address '0xB0FF_1000 [ 4K ]'. Master segment '/zynq_ultra_ps_e_0/Data/SEG_EdgeBusIP_Reg0_1' is invalid. The proposed logical address '0xB0FF_1000 [ 4K ]' remaps to physical address '0x0000_0000 [ 4K ]' which must be equivalent to the physical fixed address '0xB0FF_1000 [ 4K ]' of slave segment '/EdgeBusIP/S_AXI_LITE_TX_DMAC/Reg0'. Please assign a physical offset whose '32' least significant bits match '0xB0FF_1000'.

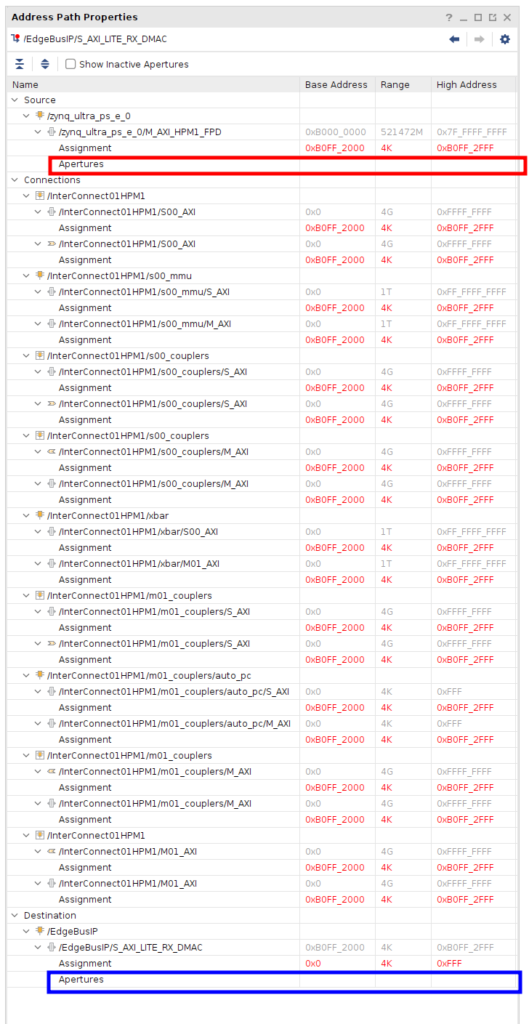

The aperture of the source(master) for /EdgeBusIP/S_AXI_LITE_DMAC is missing at red rectangle. In result, the aperture to the destination(slave) in blue rectangle is missing. I exported this map to excel file and enter aperture(0xBFFF_FFFF) for the Source in Excel and tried to import it back but it didn’t work.

- EdgeBusIPの元となるSerialBus_Wrapper.bdをSerialBus_Wrapper.hwdefファイル内にzipされていたSerialBus_Wrapper_bd.tclを使ってVivado2017.4で再生成。

- SerialBus_Wrapper.bdは、そのままではVivado2023.1にAdd Sources出来なかった。 Add Sources実行すると何かのIPバージョン4.1がないと表示されたので、そのIP名を検索して、xml形式ファイル内いで4.0だったところを2,3箇所4.1に変更したら、Vivado2023.1に取り込めた。

- そのSerialBus_Wrapper.bdを元にCreate and Package New IPして、S_AXI_LITE_RX_DMAC等のMaster Base Addressを入れてIPを新たにパッケージして、メインのBDで再接続したが同じエラーとなった。

- もとのSerialBus_Wrapper.bdを見ていると、S_AXI_LITE_RX_DMACのMaster Base Addressは0x000となっていて,0xB0FF_2000を入力しても、0x000に戻されてしまう。

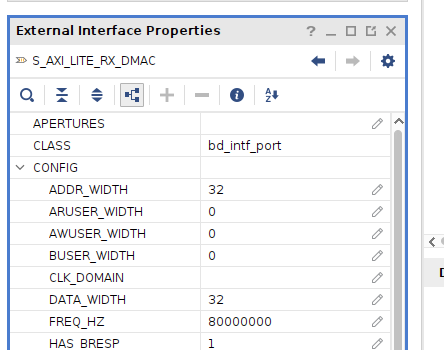

- 他のポートのアドレス幅は32ビットでS_AXI_LITE_RX_DMACとS_AXI_LITE_TX_DMACは12ビットになっているのでそれを32ビットに変更した。

- 変更する箇所は、ブロックでなく、外部接続のポートのPropertyのCONFIGのADD_WIDTHを32に変更した。

するとSerialBus_Wrapper.bdのS_AXI_LITE_RX_DMACとS_AXI_LITE_TX_DMACのベースアドレスを設定できた。

Create and Package New IPをすると、前回はBase Addressが0x000だったのに、ちゃんと0xB0FF_2000が入っている。

これを再接続したらValidateは通ったけどSynthesisで何かがloclparamとなってエラーで止まった。 まだ先は長そう。

Critital Warning IOB=TRUE 修正

./fpga/WorkDir/ip/WorkDir_HscIP_0/src/BUS_CHG/BUS_CHG.xdcを変更

set_property IOB TRUE をIOB FALSEにした。

Implementationのログファイル、./fpga/WorkDir/SUMAMO.runs/impl_1/runme.logで確認。

Critical Warningは消えたがエラーはいっこうに減らず。

./TopSumamo05.xdcには上記の対象ポートに全てIOB FALSEと設定されていたが、TopSumamo05.xdcは使用されず何故かBUS_CHG.xdcが使用された。 もしかしたら、IOB FALSE記述の前にエラーが発生して採用されなかったのかもしれない。

コメント