始める前にハードウェア構成を確認して、接続ケーブルも作成しておきます。 電源や専用接続ボードを既に持っていれば読み飛ばして下さい。

ハードウェア構成

Ultra96 v2 回路図を見てUltra96V2のハード構成図を作りました。

他の人が作ってくれていたUltra96V1の構成図もあったのですが、Ultra96V2の構成は、LEDやSW等V1と番号など色々と変わっているので作り直しました。

今回、私の場合vaddを試してみる時に必要になりそうなのは3点なので、これらについて見ていきます。

- 電源

- 極性

- 許容電圧

- 電流容量

- プラグ形状

- UART(電圧、ピン配、寸法)

- JTAG(Ultra96V2側のピン配、寸法、実際のコネクタの向き、DigilentのJTAG-HS3ケーブルのコネクタ側のピン配、コネクタに刺さるコネクタを探す)

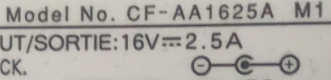

電源 8~16Vdc

回路図にかかれていた品番PJ1-021-SMT-TRの寸法図から、内径Φ5.2でプラグの外径は4.75mm以上あればいいみたい。 ピンはΦ1.65だけど内径1.7mmのプラグで2A以上対応しているものが必要。(EIA-3)

Technical Specification のPowerには12VDCと書かれているけど、回路図には+8v-16VINと書かれているので、もしかしたら電源買わなくても余っているパナのレッツノートの電源でも使えるかな。 絶対定格ならやばいけど。 極性はマッチしていますね。(結局、Avnetの電源を使用したので結果は解りません。) 因みにAVNETの専用電源は12Vです。

その他の電源供給方法

- 部品は半田付しないといけませんがJP1のピン経由で直接入力する方法もある。 D20も必要。

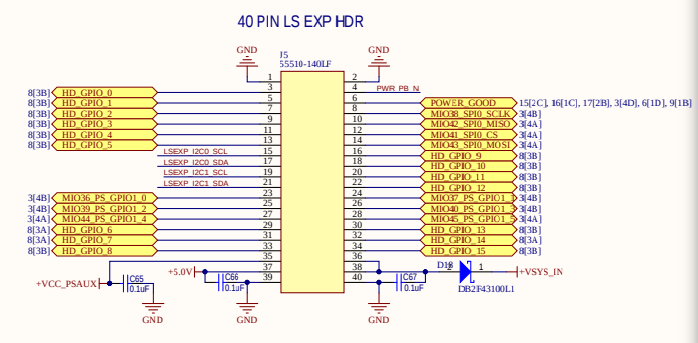

- 或いは、J5 Low Speed expansion headerのpin36&38(両方12Vdc)とpin40(GND)を使う。

電源名と電圧(回路図内)

UARTやJTAGの電圧を知る時に参照できるように、回路図から信号別の電圧を拾ってきます。(使わないかもしれないけど、と思ったら案の定+VCC_PSAUXは参考になりました。)

- +VCC_PSINTLP — 0.85V 0.3A

- +VCC_PSINTFP — 0.85V 3.0A

- +VCC_PSPLL —1.20V 0.5A

- +VCC_PSAUX —1.80V 1.0A

- +3.3V —3.30V 1.3A

- +MGTRAVCC —0.90V 0.3A

- +MGTRAVTT —1.80V 0.03A

通信(UART、JTAG)

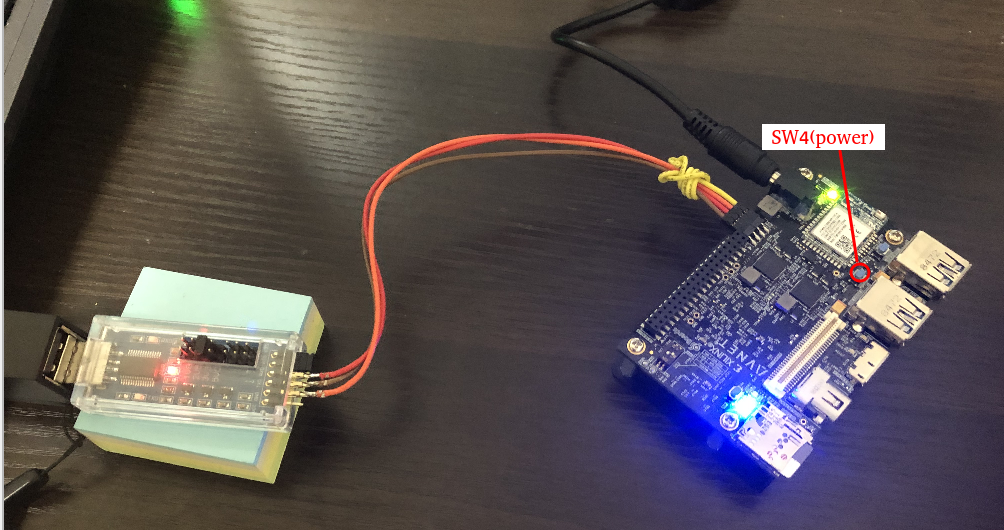

Ultra96V2のJTAGやUARTへのアクセスには、Avnetが提供しているAES-ACC-U96-JTAGボード(8000円程度)を使うのが一番簡単みたいですが、Ultra96V2以外のボードでは使用でき無さそうな事と、UART変換器は既に持っているので、将来他の基板でも使えるように、持っているUART変換器やJTAG-HS3でUltra96V2と通信出来る様にケーブルを作ってみようと思います。 AES-ACC-U96-JTAGボードを使う場合は以下は不要です。

UART通信 (J1) +3.3V

FPGA設定用のビットストリームファイルは、microSDからFPGAに転送したのでJTAGはまだ使っていませんが、UARTはKernelメッセージを見てデバッグする際に絶対に必要です。

Ultra96V2のUARTも回路図を見たらJ1で4pinコネクタ。 miniQI規格の2.0mmピッチで 接続は1~3の3ピンでいい。

- MIO1_UART1_RX ⇐ TX(USB-UART変換器)

- MIO1_UART1_TX ⇒ RX(USB-UART変換器)

- GND ⇔ GND(USB-UART変換器)

- +3.3V(Pull up) 未接続

Ultra96V2の4pinコネクタも2mmピッチなので、下の図の様な共立電子産業製のミニQIケーブル4S-Zケーブルをモノタロウから買って使います。 ケーブルの線の番号は抵抗のカラーコードとピン番号を合わせた色の線になっています。 私は、ノイズ等の影響がでたら嫌なのでこのケーブルを半分に切って短くして使いました。

このケーブルをBeaglebone Blackで使った、DSD TECH SH-U09C5 USB to TTL UARTコンバーター( FTDIチップサポート付き 5V 3.3V 2.5V 1.8V TTLサポート)の2.54mmピッチの線にMIL 4pinコネクタで配線することにします。

- こんな感じでミニQIケーブルのコネクタはUltra96V2のUARTコネクタに綺麗に刺さってます。

- UART-USB変換器の方は、QIコンタクトピン(メス)を裸の状態で挿しています。 ケーブルの線がAWG24で、コンタクトピンをかしめたら、QIコネクタに差し込めなかったのです。(専用工具を使ったら差し込めるかもしれませんが、私はラジオペンチでかしめたのですがヘボすぎたのかもしれません。)

ちゃんと通信しています。

JTAG(J3:MMT-108-01-T-SH-LC) +VCC_PSAUX(1.8V)

*JTAGは、まだ使っていないので検証出来ていません。 使える確認が出来たら更新します。

Ultra96V2のJTAGも回路図を見たらJ3で8pinコネクタ。 ミニQIの2.0mmピッチ。 Avnetに確認したら、UART J1コネクタに近い方が1番ピンとの事。

- VCC_PSAUX –Vcca–VDD1…1.8V

- GND

- JTAG_TCK

- JTAG_TMS

- JTAG_TDI

- PS_SRST_N —PS部のシステムリセット。JTAG経由で再起動出来るはず。

- JTAG_TDO

- PS_POR_N — PS部のPower On中のリセット。 このピンは未接続でSW2を使います。 JTAG-HS3からは供給されません。

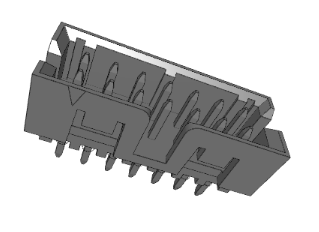

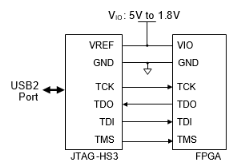

Digilent製 JTAG-HS3との接続

ボードとの接続は2mmピッチの2列x7ピンの14ピンコネクタなので、通常の2.54mmピッチのコネクタやバラ線が接続できません。

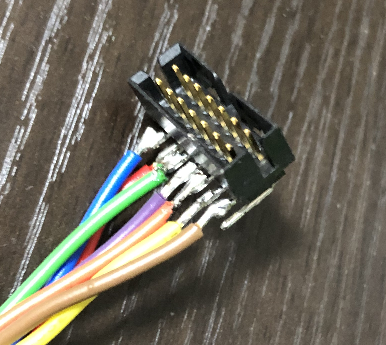

なので、JTAG-HS3の2mmピッチの2列x7ピンの14ピンコネクタには、Molex 87831-1420を買ったので、裏の端子に半田付けしようと思います。

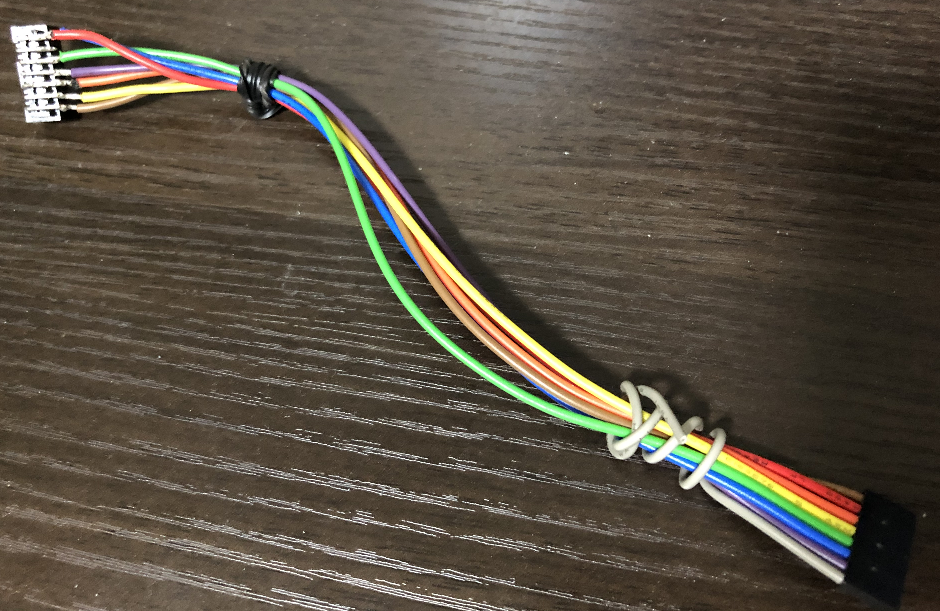

Ultra96V2の8ピンへの接続もミニQIで2mmピッチなので、ミニQIのコネクタ付き共立電子産業製のミニQIケーブル8S-Zを使います。 これも線は半分に切りました。

ミニQIケーブル8S-Zの線は抵抗のカラーコードと同じになっています。 JTAG-HS3の7×2ピンメスコネクタに刺さるMolexオスコネクタの裏面のピンに半田付するため、コネクタの裏面から見たピン配。

以下のように、Molex 87831-1420に線を半田付けしました。 写真がぼやけて見えにくいのですが、Molex 87831-1420はRight Angleタイプで90度曲がっていて、はんだ付けしているのは1本(赤線)を除いて全て下段にしているので、はんだ付けはちょっと面倒でした。 灰色の線は今回見せつ

ヘボ半田ですが、ちゃんと付いています。 赤線だけが、別の列に付けられています。 2.0mmピッチの2段は難しい。 角度を変えて固定できるものと、照明付き拡大鏡を使いました。

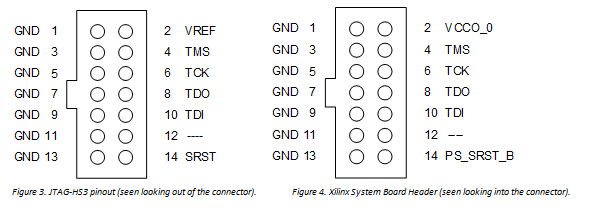

- 下の図はDigilentの資料のJTAG-HS3のピン配置

- 左図(Figure3)はJTAG-HS3側で、コネクタの根本から見たピン配置。

- これはややこしいです。 なのでコネクタの穴に向かって覗き込むと、上下が反転します。

- 右図(Figure4)は、AVNET製Ultra96V2でないく、Xilinx製ボードのピン配置で、JTAGコネクタに向かって見た場合のピン配置です。

- これで、左図と右図の信号が一致しています。

上記を元に接続していきます。

- 左の1~8はミニQIケーブル8S-Zの8pinコネクタの番号です。

- 右の『—番号』は、Molex 87831-1420(=JTAG-HS3の14ピンコネクタ)のピン番号

- VCC_PSAUX –Vcca–VDD1…1.8V(茶)—2

- GND (赤)—13

- JTAG_TCK (オレンジ)—6

- JTAG_TMS (黄) —-4

- JTAG_TDI (緑) —-10

- PS_SRST_N (青)—-14

- JTAG_TDO (紫)—- 8

- PS_POR_N — 接続しない (灰)

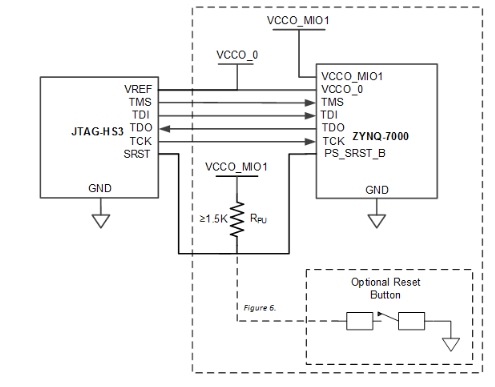

以下のDigilentのマニュアルの回路図を接続を再確認。 JTAGの場合、UARTと違って、TDIはTDI、TDOはTDOに接続するみたい。 更に、VREFもVCCに接続するみたいなので、その様に配線します。 上の図はSoC用(Zynqなど)、下の図はFPGA用のようです。

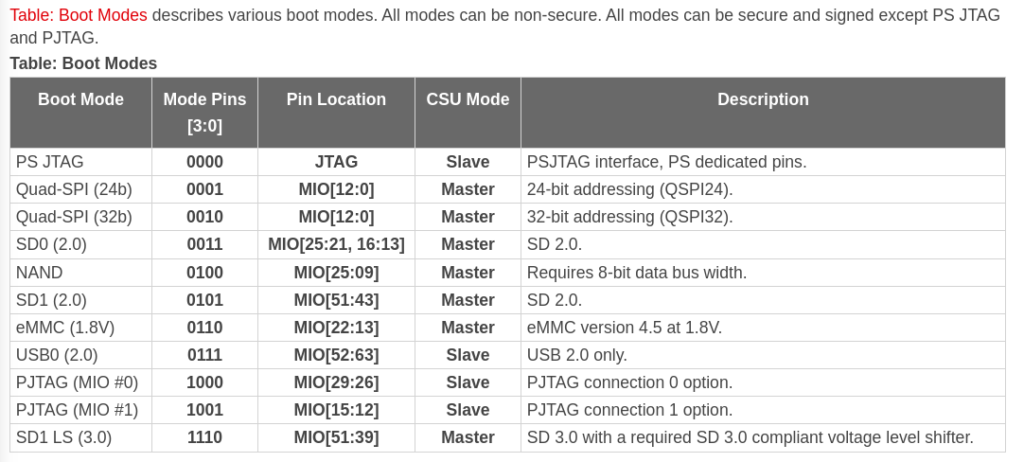

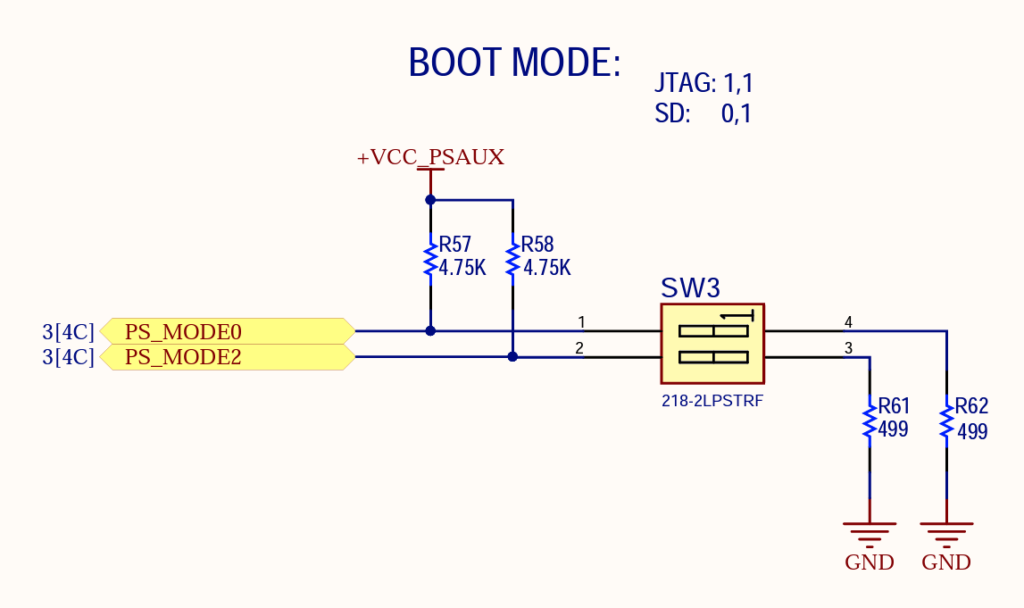

ブートMODE

SD起動かJTAG起動しかできないようです。 USB0は使い方が分かりませんが、もしかしたらできるかもしれません。

以下はXilinx UG1085から引用したZynq UltraScale+のブートモードです。 PS_MODE[3:0]につながっています。 UltraScale96V2はsw3でPS_MODE0とPS_MODE2を切り替えれますが、基板上でPS_MODE1はPS_MODE0接続されていて、PS_MODE3は常時『0(High)』です。なので以下の様になると思います。

- 2/1

- OFF / OFF(0111) ーーーUSB0

- OFF / ON (0100) ーーーNAND—Ultra96V2には無いと思います

- ON / OFF (0011) ーーーSD0

- ON / ON (0000) ーーーJTAG

おしまい

参考

ここから下は将来に使うかもしれないのでメモです。

Ultra96搭載

- 電源12V 4A Φ1.7(標準のΦ2.1からΦ1.7への変換プラグアダプタが必要)

- 極性:外側がGND

- 802.111b/g/n Wifi+bluetooth

- microSD SDXC みたいなので最大128GB(eMMCは無いみたい)

- 2GB LPDDR4

- mini DisplayPort 4K —HDMI変換はアクティブ変換タイプか安いこれが必要

- USB3.0 Micro-B slave x 1

- USB3.0 Type-A host x 2

- 40pin header

- 60pin high speed connector

- J1 4pin UART header(3.3V)

- MIO1_UART1_RX

- MIO1_UART1_TX

- GND

- MMT-104-01-T-SH-1 —-コネクタの品番

- JTAG J3

- VCC_PSAUX –Vcca–VDD1…1.8V

- GND

- JTAG_TCK

- JTAG_TMS

- JTAG_TDI

- PS_SRST_N

- JTAG_TDO

- PS_POR_N — not connected

microSDカードにイメージファイルをダウンロードして立ち上げなければなりません。

Ultra96で使用されているZynq UltraScale+ ZU3EG-A484

Zynq UltraScale+ MPSoC ZU3EG A484

- Cortex-A53 (64/32bit) 1.5GHz x 4 core

- Cortex-R5F 600MHz x 2 core

- GPU Mali-400 667MHz

- DDR4, LPDDR4, DDR3, DDR3L, LPDDR3

- PCIe Gen3x8 2ch or Gen3x16 1ch

- Logic cell 157k

- LUTs 70k

- 総RAM 9.4MB(Distributed RAM 1.8MB、Block RAM 7.6MB w/216 blocks)

- supports all Zynq SDHC, MP/Versal SDXC

Zynq Ultrascale+ selection guide

メモリーマップ

DDRにアクセスする際に必要になると思うので読みやすいように作成。

- DDR4 SDRAM: 0x0000_0000 to 0x7FFF_FFFF (2 GB)

- PCIe memory: 0x8000_0000 to 0x9FFF_FFFF (512 MB)

- Peripherals:

- AFI: 0xA000_0000 to 0xA00F_FFFF (1 MB)—-Ultra96V2の場合、AFIはQSPI接続のeMMCのはずで、0x0から64MBのはず。

- GIC: 0xF900_0000 to 0xF900_0FFF (4 KB)

- UART: 0xFF00_0000 to 0xFF00_0FFF (4 KB)

- WDT: 0xFF5E_0000 to 0xFF5E_0FFF (4 KB)

- TTC: 0xFF110000 to 0xFF11_0FFF (4 KB)

- I2C: 0xFF020000 to 0xFF02_0FFF (4 KB)

- GPIO: 0xE000_0000 to 0xE000_0FFF (4 KB)

- SPI: 0xE000_4000 to 0xE000_4FFF (4 KB)

- Ethernet: 0xE000_0000 to 0xE000_0FFF (4 KB)

Global System Address Map

| スレーブ名 | 容量 | 開始アドレス | アドレス幅 |

|---|---|---|---|

| Reserved | 256 GB | 0x00C0_0000_0000 | 40bit |

| PCIe High | 256 GB | 0x0080_0000_0000 | |

| M_AXI_HPM1_FPD (HPM1) | 224 GB | 0x0048_0000_0000 | |

| M_AXI_HPM0_FPD (HPM0) | 224 GB | 0x0010_0000_0000 | |

| DDR High Memory Controller | 32 GB | 0x0008_0000_0000 | 36bit/40bit |

| PCIe High | 8 GB | 0x0006_0000_0000 | |

| M_AXI_HPM1_FPD (HPM1) | 4 GB | 0x0005_0000_0000 | |

| M_AXI_HPM0_FPD (HPM0) | 4 GB | 0x0004_0000_0000 | |

| Reserved | 12 GB | 0x0001_0000_0000 | |

| CSU, PMU, TCM, OCM | 4 MB | 0xFFC0_0000 | 32bit/36bit/40bit |

| Lower LPD slaves | 12 MB | 0xFF00_0000 | |

| Upper LPD slaves | 16 MB | 0xFE00_0000 | |

| FPD slaves | 16 MB | 0xFD00_0000 | |

| Reserved | 63 MB | 0xF910_0000 | |

| APU GIC | 1 MB | 0xF900_0000 | |

| STM CoreSight | 16 MB | 0xF800_0000 | |

| Reserved | 128 MB | 0xF000_0000 | |

| PCIe Low | 256 MB | 0xE000_0000 | |

| Quad-SPI | 512 MB | 0xC000_0000 | |

| M_AXI_HPM1_FPD (HPM1) interface | 256 MB | 0xB000_0000 | |

| M_AXI_HPM0_FPD (HPM0) interface(1) | 192 MB | 0xA400_0000 | |

| VCU Slave(1) | 64 MB | 0xA000_0000 | |

| M_AXI_HPM0_LPD (LPD_PL) | 512 MB | 0x8000_0000 | |

| DDR Low Memory Controller | 2 GB | 0x0000_0000 |

各種レジスタアドレスやBoot 設定等も以下のリンクの下に書かれている。

Wifi設定

以下のように書いたらいいみたいだけど、自分でビルドしたLinuxではwifi.shもなかった。 何処に記述下来のかもわからない。 先にデバイスツリーsystem-user.dtsiに追記して、以下も記述しないといけないかもしれない。 今後の参考メモ。

$ vi wpa_supplicant.conf

ctrl_interface=/var/run/wpa_supplicant

ctrl_interface_group=0

update_config=1

network={

key_mgmt=WPA-PSK

ssid=""

psk=""

}

$ ./wifi.sh

USB g_ether接続

USBでEthernet用プロトコルを使用する場合に使いますが、今回は使えていません。 将来のメモに残しておきます。

$ modprobe g_ether $ ifconfig // ifconfig <IP_ADDR> up でもいいかもしれない。

ケーブルの抵抗カラーコード

入社したての頃一生懸命覚えました。

- 黒 (ピン0はないので使われていない。 しかし、10ピン目や20ピン目に使われると思う)

- 茶 —ピン1

- 赤 —ピン2

- 橙 —ピン3

- 黄 —ピン4

- 緑 —ピン5

- 青 —ピン6

- 紫 —ピン7

- 灰 —ピン8

- 白 (今回、8ピンまでしかないので使われていない。 9や19や29ピン目に使われる)

ultra96v2 dts

使いませんでしたが、一応参考まで。

コメント